## ESE | GATE | PSUs

### ELECTRONICS & TELECOMMUNICATION ENGINEERING

DIGITAL CIRCUITS & MICROPROCESSORS

Text Book : Theory with worked out Examples and Practice Questions Number Systems

(Solutions for Text Book Practice Questions)

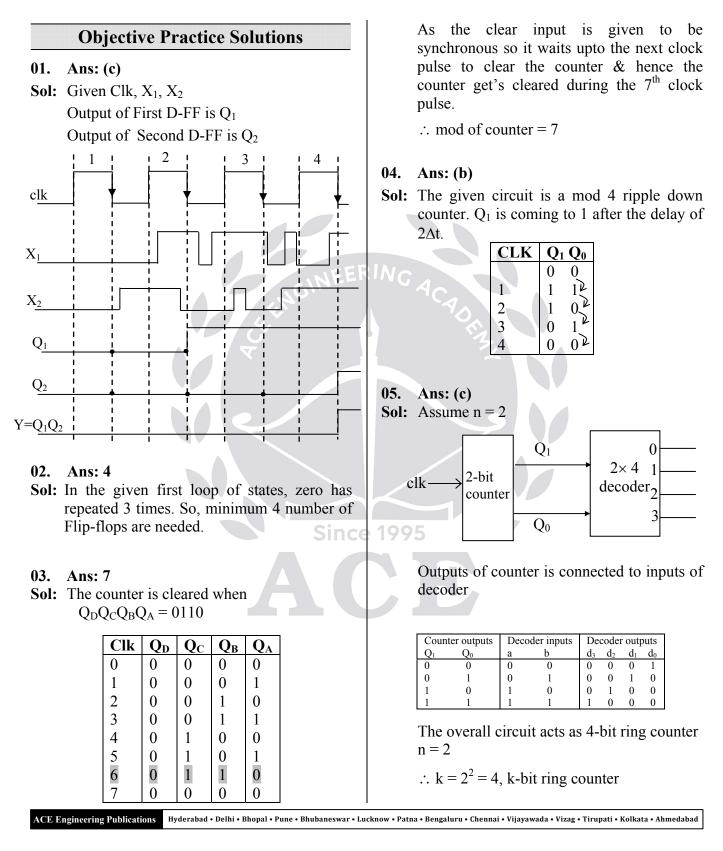

#### **Objective Practice Solutions**

#### 01. Ans: (d)

Chapter 🔛 |

Sol:  $135_x + 144_x = 323_x$   $(1 \times x^2 + 3 \times x^1 + 5 \times x^0) + (1 \times x^2 + 4 \times x^1 + 4 \times x^0)$   $= 3x^2 + 2x^1 + 3x^0$   $\Rightarrow x^2 + 3x + 5 + x^2 + 4x + 4 = 3x^2 + 2x + 3$   $x^2 - 5x - 6 = 0$  (x-6) (x+1) = 0 (Base cannot be negative) Hence x = 6.

#### (OR)

As per the given number x must be greater than 5. Let consider x = 6

$(135)_6 = (59)_{10}$

$(144)_6 = (64)_{10}$

$(323)_6 = (123)_{10}$

$(59)_{10} + (64)_{10} = (123)_{10}$ So that x = 6

#### 02. Ans: (a)

Sol: 8-bit representation of

$+127_{10} = 01111111_{(2)}$

1's complement representation of

-127 = 10000000.

2's complement representation of

-127 = 10000001.

No. of 1's in 2's complement of

$$-127 = m = 2$$

No. of 1's in 1's complement of

-127 = n = 1

$\therefore$  m: n = 2:1

#### 03. Ans: (c)

Sol: In 2's complement representation the sign bit can be extended towards left any number of times without changing the value. In given number the sign bit is ' $X_3$ ', hence it can be extended left any number of times.

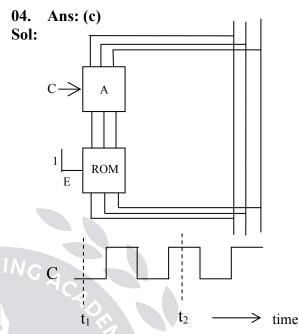

#### 04. Ans: (c)

**Sol:** Binary representation of  $+(539)_{10}$ :

|             | 1.00        |     |  |

|-------------|-------------|-----|--|

| 2           | 539         |     |  |

| 2<br>2<br>2 | 269         | -1  |  |

|             | 134         | -1  |  |

| 2<br 2<br>2 | 67          | -0  |  |

| 2           | 33          | -1  |  |

| 2           | 16          | -1  |  |

| 2           | 8           | 0   |  |

| 2           | 4           | _0_ |  |

| 2           | 8<br>4<br>2 | -0  |  |

|             | 1           | -0  |  |

$(+539)_{10} = (10000 \ 11 \ 0 \ 11)_2 = (00100 \ 0011011)_2$ 2's complement  $\rightarrow 110111100101$

Hexadecimal equivalent  $\rightarrow$  (DE5)<sub>H</sub>

#### 05. Ans: 5

Since

Sol: Symbols used in this equation are 0,1,2,3 Hence base or radix can be 4 or higher  $(312)_x = (20)_x (13.1)_x$   $3x^2 + 1x^1 + 2x^0 = (2x^1+0) (x+3x^0+x^{-1})$   $3x^2 + x + 2 = (2x) \left(x+3+\frac{1}{x}\right)$   $3x^2 + x + 2 = 2x^2 + 6x + 2$   $x^2 - 5x = 0$  x(x-5) = 0 x = 0(or) x = 5x must be x > 3, So x = 5

|       | ACE<br>Engineering Publications                                                               | 3      |          | Digital & Microprocessors                                                                        |

|-------|-----------------------------------------------------------------------------------------------|--------|----------|--------------------------------------------------------------------------------------------------|

| 06.   | Ans: 3                                                                                        | 0      | )9.      | Ans: (b)                                                                                         |

| Sol:  | $123_5 = x8_y$                                                                                | S      | Sol:     | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                             |

|       | $1 \times 5^2 + 2 \times 5^1 + 3 \times 5^0 = x.y^1 + 8 \times y^0$                           |        |          | $\star$ $\star$ $\star$ $\star$                                                                  |

|       | 25 + 10 + 3 = xy + 8                                                                          |        |          | (111 101) (110 101)                                                                              |

|       | $\therefore xy = 30$                                                                          |        |          | C. 3 7 D. 2 6 $\downarrow$ $\downarrow$ $\downarrow$ $\downarrow$ $\downarrow$                   |

|       | Possible solutions:                                                                           |        |          | $\begin{array}{ccc} \downarrow & \downarrow & \downarrow \\ (011\ 111) & (010\ 110) \end{array}$ |

|       | i. $x = 1, y = 30$                                                                            |        |          |                                                                                                  |

|       | ii. $x = 2, y = 15$<br>iii. $x = 3, y = 10$                                                   | 1      | 0.       | Ans: (a)                                                                                         |

|       | $\therefore$ 3 possible solutions exists.                                                     |        |          | 2's complement arithmetic is preferred in                                                        |

| 07.   | Ans: 1                                                                                        |        |          | digital computers because it is efficient and one representation for zero.                       |

| Sol:  | The range (or) distinct values                                                                |        |          |                                                                                                  |

|       | For 2's complement $\Rightarrow -(2^{n-1})$ to $+(2^{n-1}-1)$                                 | - 1    | 1.       | Ans: (a)                                                                                         |

|       | GIN                                                                                           | S      | Sol:     | $(11X1Y)_8 = (12C9)_{16}$                                                                        |

|       | For sign magnitude                                                                            | A.     |          | $8^4 + 8^3 + 8^2 X + 8 + Y$                                                                      |

|       | $\Rightarrow -(2^{n-1}-1) \text{ to } +(2^{n-1}-1)$                                           |        |          | $= 16^3 + (2 \times 16^2) + (12 \times 16) + 9$                                                  |

|       | Let $n = 2 \Rightarrow$ in 2's complement                                                     |        |          | 4096 + 512 + 64X + 8 + Y                                                                         |

|       | $-(2^{2-1})$ to $+(2^{2-1}-1)$                                                                |        |          |                                                                                                  |

|       | $-2$ to $+1 \Rightarrow -2, -1, 0, +1 \Rightarrow X = 4$                                      |        |          | =4096+512+192+9                                                                                  |

|       | $n = 2$ in sign magnitude $\Rightarrow -1$ to $+1 \Rightarrow Y = 3$                          |        |          | $\therefore 4616 + 64X + Y = 4809$                                                               |

|       | X - Y = 1                                                                                     |        |          | 64X + Y = 193                                                                                    |

|       |                                                                                               |        |          | By verification option (a) is correct.                                                           |

| 08.   | Ans: (c)                                                                                      |        |          |                                                                                                  |

| Sol:  | (a) $(68)_{16} = (001 \ 101 \ 000)_2$ Sinc                                                    | e 1    | 2.9      | Ans: (d)                                                                                         |

|       | $= (1  5  0)_8$                                                                               | S      | Sol:     | 2's comp no: $a_3 a_2 a_1 a_0$                                                                   |

|       | (b) $(8C)_{16} = (010 \ 001 \ 100)_2$                                                         |        |          |                                                                                                  |

|       | (b) $(8C)_{16} = (\begin{array}{c} 010 \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$ |        |          | 2's comp no. using 6 bits                                                                        |

|       | $= (2 \ 1 \ 4)_8$                                                                             |        |          |                                                                                                  |

|       | (c) $(4F)_{16} = (001\ 001\ 111\ )_2$<br>= $(1\ 1\ 7)_8$                                      |        |          | $\rightarrow \qquad a_3 \ a_3 \ a_3 \ a_2 \ a_1 \ a_0$                                           |

|       | $= (1 \ 1 \ 7)_8$                                                                             |        |          | (2's comp no)× 2 + 1                                                                             |

|       | (d) $(5D)_{16} = (001\ 011\ 101\ )_2$<br>= $(1\ 3\ 5\ )_8$                                    |        |          | $\rightarrow \qquad a_3 \ a_3 \ a_2 \ a_1 \ a_0 \ 1$                                             |

| ACE E | ngincering Publications Hyderabad • Delhi • Bhopal • Pune • Bhubaneswar •                     | ucknow | v • Patı | na • Bengaluru • Chennai • Vijayawada • Vizag • Tirupati • Kolkata • Ahmedabad                   |

| ACE<br>Engineering Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4 Postal Coaching Solutions                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Conventional Practice Solutions</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 03.<br>Sol:                                                                                                                                                                                                                                                                                                                                                                   |

| 01.<br>Sol:<br>1) $110.01 + 1.011$<br>= 110.010<br>$\frac{1.011}{111.101}$<br>= 111.101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | i) $(1A53)_{16} = (1 \times 16^3) + (10 \times 16^2)$<br>$+ (5 \times 16) + (3 \times 16^\circ)$<br>= 4096 + 2560 + 80 + 3<br>$= (6739)_{10}$<br>ii) $(93)_{16} = (147)_{10}, (DE)_{16} = (222)_{10}$<br>$(93)_{16} + (DE)_{16} = 147 + 222 = (369)_{10}$<br>$= (171)_{16}$<br>iii) $(11010)_2$<br>$= 1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2 + 0 \times 2^0$ |

| 2) $(11101.01)_2$<br>= $(1 \times 2^4 + 1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0)$<br>+ $(0 \times 2^{-1}) + (1 \times 2^{-2})$<br>= $16 + 8 + 4 + 1 + 0.25$<br>= $(29.25)_{10}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $= 1 \times 2 + 1 \times 2 + 0 \times 2 + 1 \times 2 + 0 \times 2$ $= 16 + 8 + 0 + 2 + 0 = 26$                                                                                                                                                                                                                                                                                |

| <ul> <li>3) 11100.101 - 101.01 <ul> <li>11100.101</li> <li><u>11010.110</u> (2's complement of 101.01 is)</li> <li>10111.011</li> </ul> </li> <li>4) Convert (111000)<sub>2</sub> to octal <ul> <li>= 111 000</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |

| $=(70)_{\circ}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e 1995                                                                                                                                                                                                                                                                                                                                                                        |

| $(A5F1)_{16} = (1010 \ 0101 \ 1111 \ 0001)_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                               |

| $= (001 \ 010 \ 010 \ 010 \ 111 \ 110 \ 001)_2$ $= (001 \ 010 \ 010 \ 111 \ 110 \ 001)_2$ $= (001 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 010 \ 0$ |                                                                                                                                                                                                                                                                                                                                                                               |

| $=(1\ 2\ 2\ 7\ 6\ 1)_8$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                               |

| ACE Engineering Publications Hyderabad • Delhi • Bhopal • Pune • Bhubaneswar •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Lucknow • Patna • Bengaluru • Chennai • Vijayawada • Vizag • Tirupati • Kolkata • Ahmedabad                                                                                                                                                                                                                                                                                   |

# Chapter 2

### Logic Gates & Boolean Algebra

| Engineering Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                    | Digital & Microprocessors                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13. Ans: (b)<br>Sol: (A) $ab + bc + ca + abc$<br>bc (1 + a) + ca + ab<br>bc + ca + ab<br>Inverse function $(\overline{ab + bc + ca})$<br>$= \overline{a} \ \overline{b} + \overline{b} \ \overline{c} + \overline{c} \ \overline{a}$<br>(B) $ab + \overline{a} \ \overline{b} + \overline{c}$<br>Inverse function $= \overline{ab + \overline{a} \ \overline{b} + \overline{c}}$<br>$= (\overline{a} + \overline{b}) (a + b) c$<br>$= (\overline{a} + \overline{b}) c$<br>$= (\overline{a} + b) c$<br>(C) $(a + bc)$<br>Inverse function $= \overline{a + bc}$ |                      | <ul> <li><b>16.</b> Ans: (c)</li> <li><b>Sol:</b> A NAND gate represents a universal logic family.</li> <li>Only two NAND gates are sufficient to accomplish any of the basic gates.</li> <li>Statement-I is true but statement-II is false.</li> </ul> |

| $= \overline{a}(\overline{b} + \overline{c})$ (D) $(\overline{a} + \overline{b} + \overline{c})(a + \overline{b} + \overline{c})(\overline{a} + \overline{b} + c)$ Inverse function $\overline{(\overline{a} + \overline{b} + \overline{c})(a + \overline{b} + \overline{c})(\overline{a} + \overline{b} + c)}$                                                                                                                                                                                                                                                |                      |                                                                                                                                                                                                                                                         |

| $(\overline{a} + \overline{b} + \overline{c})(a + \overline{b} + \overline{c})(\overline{a} + \overline{b} + c)$<br>= $abc + \overline{a}bc + ab\overline{c}$<br>14. Ans: (c)<br>Sol: AND gate : Boolean multiplication<br>OR gate : Boolean addition<br>NOT gate : Boolean complementation                                                                                                                                                                                                                                                                    | ice 1                | 995<br>E                                                                                                                                                                                                                                                |

| <ul> <li>15. Ans: (a)</li> <li>Sol: When all inputs of a NAND-gate a shorted to get a one input, one output gat it becomes an inverter.<br/>When all inputs of a NAND-gate are logic '0' level, the output is at logic ' level.<br/>Both statements are true and statement-II the correct explanation of statement-I.</li> </ul>                                                                                                                                                                                                                               | e,<br>at<br>1'<br>is | w • Patna • Bengaluru • Chennai • Vijayawada • Vizag • Tirupati • Kolkata • Ahmedabad                                                                                                                                                                   |

### ACE

#### **Conventional Practice Solutions**

#### 01.

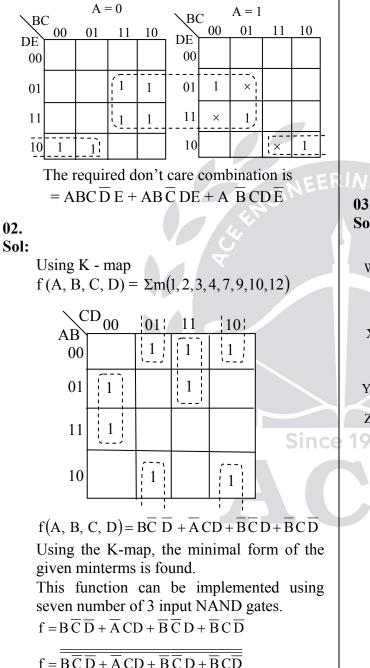

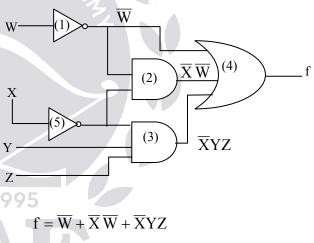

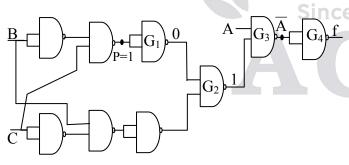

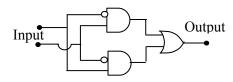

Sol: The given don't care & expression can be realized as follows:

The circuitry for above minimal expression using NAND gates as follows. Let us assume that variables are available in complement form also.

03.

Sol:

$$= \overline{W}[1 + \overline{X}] + \overline{X}YZ$$

$$= \overline{W} + \overline{X}YZ$$

Thus from expression for the output f, WE can conclude that gate no.(2) is redundant and even if the gate is removed from the circuit the output expression is

$$f = \overline{W} + \overline{X}YZ$$

f

ACE Engineering Publications Hyderabad • Delhi • Bhopal • Pune • Bhubaneswar • Lucknow • Patna • Bengaluru • Chennai • Vijavawada • Vizag • Tirupati • Kolkata • Ahmedabad

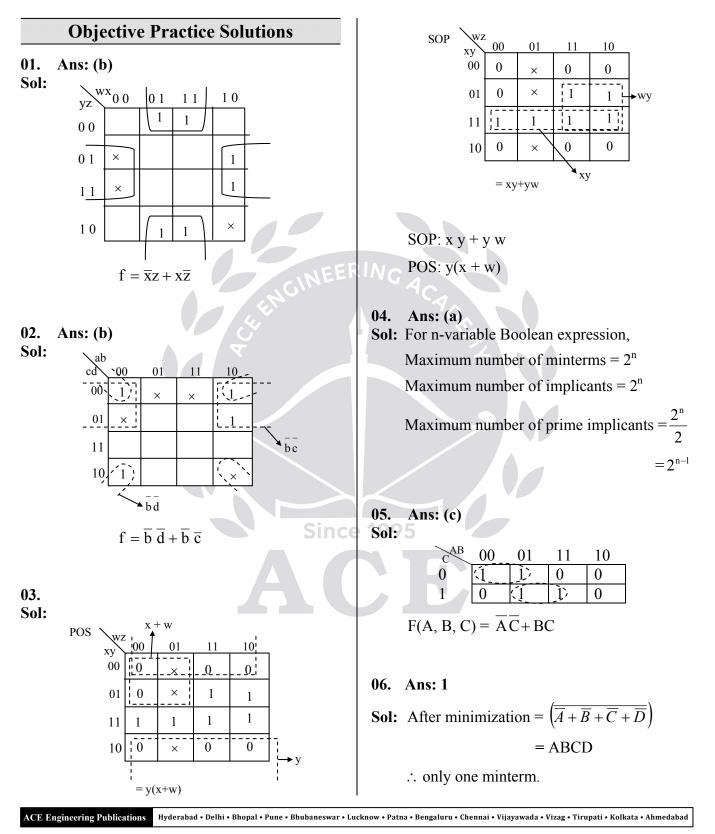

## K - Maps

$\therefore$  Total number of prime implicants of the function 'f' is 3.

No. of essential prime implicants = 4.

**Postal Coaching Solutions**

#### **Conventional Practice Solutions**

#### 01.

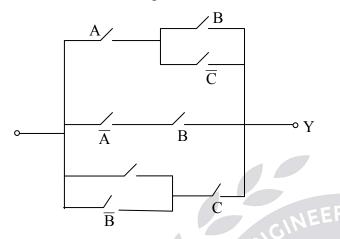

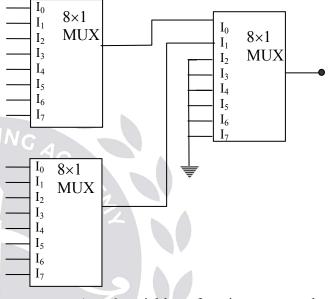

Sol: Given circuit diagram is

Series combination: AND gate Parallel combination: OR gate  $Y = A(B + \overline{C}) + \overline{A}B + (A + \overline{B})C$  $= AB + A\overline{C} + \overline{A}B + AC + \overline{B}C$  $= B(A + \overline{A}) + A\overline{C} + AC + \overline{B}C$  $= B + A + \overline{B}C = A + B + C$

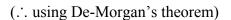

02.

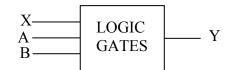

**Sol:** The circuit diagram gives in the question is redrawn as

Output of gate  $G_1$  will definitely be 0. If any one of the input of  $G_2$  is 0, output of  $G_2$  is definitely 1. Output of gate  $G_3 = \overline{A}$ Output of gate  $G_4$ ,  $f = \overline{\overline{A}} = A$  $\therefore f = A$

#### .. I — A ACE Engineering Publications

#### 03.

1995

Hyderabad • Delhi • Bhopal • Pune • Bhubaneswar • Lucknow • Patna • Bengaluru • Chennai • Vijavawada • Vizag • Tirupati • Kolkata • Ahmedabad

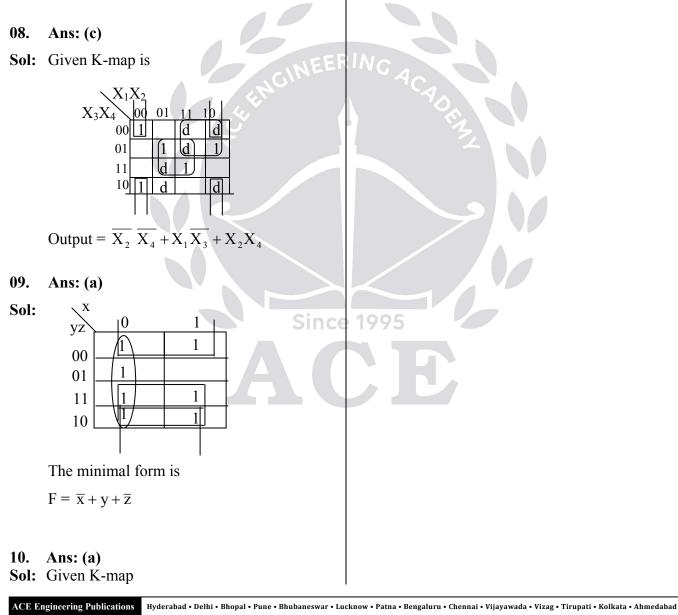

Sol: Given K-map is

| <hr/>    |     |    |    |     |   |

|----------|-----|----|----|-----|---|

| xy<br>xy | 00. | 01 | 11 | .10 | _ |

| 00       | d   |    | 0  | 1   | _ |

| 01       | 0   | 1  | d  | 0   |   |

| 11       | 1   | d  | d  | 0   |   |

| 10       | d   | 0  | 0  | d   |   |

|          |     |    |    | !   |   |

The minimized SOP expression from the given k map is

for the expression in equation (1) the Literal count = 8

| xy | v<br>00 | 01 | 11       | 10 |

|----|---------|----|----------|----|

| 00 | [đ]     | 1  | 0        | 1  |

| 01 | 0       | 1  |          | 0  |

| 11 | 1       | d  | <u>d</u> | 0  |

| 10 | ŀd      | 0  | 0        | d  |

The minimized POS expression is  $y = (\overline{x} + y)(\overline{z} + \overline{w})(\overline{y} + \overline{z})(x + z + w)$ ----- (2) For the expression in equation (2) the Literal count = 9

Chapter **Z**

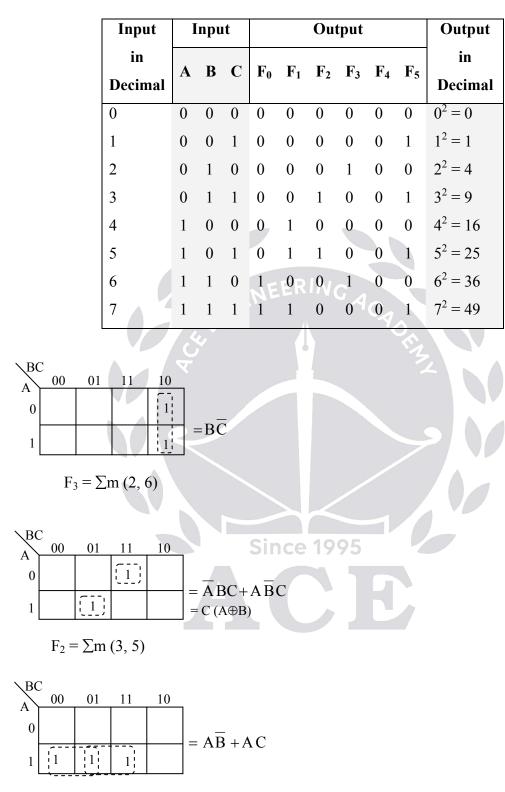

### **Combinational Circuits**

#### **Objective Practice Solutions**

#### 01. Ans: (d)

- **Sol:** Let the output of first MUX is " $F_1$ "

- $F_1 \!=\! \mathbf{A} I_0 \!\!+\! \mathbf{A} I_1$

Where A is selection line,  $I_0$ ,  $I_1 = MUX$ Inputs

$$F_1 = \overline{S}_1 \cdot W + S_1 \cdot \overline{W} = S_1 \oplus W$$

Output of second MUX is

$$F = \overline{A}.I_0 + A.I_1$$

$F = \overline{S}_2.F_1 + S_2.\overline{F}_1$

$$F = S_2 \oplus F_1$$

But  $F_1 = S_1 \oplus W$

- $F = S_2 \oplus S_1 \oplus W$

- i.e.,  $F = W \oplus S_1 \oplus S_2$

#### 02. Ans: 19.2

- **Sol:** One AND/OR gate delay =  $1.2 \ \mu s$

- One XOR gate delay  $= 2.4 \ \mu s$ Full Adder with 2 Half Adder

HA1 Since A B HA2 Sum C Carry

In one F.A; Sum delay =  $4.8 \mu s$ Carry delay =  $2.4 + 1.2 + 1.2 \mu s = 4.8 \mu s$

:. RippleCarry waiting time =  $4.8 \times 3 = 14.4 \,\mu s$

Final Result time =  $14.4 + 4.8 = 19.2 \mu sec$

#### 03. Ans: (a)

**Sol:** The given circuit is binary parallel adder/subtractor circuit. It performs A+B, A–B but not A + 1 operations.

| K | C <sub>0</sub> | Operation                                           |  |

|---|----------------|-----------------------------------------------------|--|

| 0 | 0              | A+B (addition)                                      |  |

| 0 | 1              | A+B+1(addition with carry)                          |  |

| 1 | 0              | $A + \overline{B}$ (1's complement addition)        |  |

| 1 | 1              | $A + \overline{B} + 1$ (2's complement subtraction) |  |

#### 04. Ans: (d)

Sol: It is expansion of 2:4 decoders to 1:8 demultiplexer  $A_1$ ,  $A_0$  must be connected to  $S_1$ ,  $S_0$  i.e..,  $R = S_0$ ,  $S = S_1$

Q must be connected to  $S_2$  i.e.,  $Q = S_2$

P is serial input must be connected to D<sub>in</sub>

#### 05. Ans: 6

Sol:  $T = 0 \rightarrow NOR \rightarrow MUX \ 1 \rightarrow MUX \ 2$   $2ns \quad 1.5ns \quad 1.5ns$  Delay = 2ns + 1.5ns + 1.5ns = 5ns  $T = 1 \rightarrow NOT \rightarrow MUX \ 1 \rightarrow NOR \rightarrow MUX \ 2$  $1ns \quad 1.5ns \quad 2ns \quad 1.5ns$

Delay = 1ns + 1.5ns + 2ns + 1.5ns = 6ns

Hence, the maximum delay of the circuit is 6ns.

#### 06. Ans: -1

**Sol:** When all bits in 'B' register is '1', then only it gives highest delay.

$\therefore$  '-1' in 8 bit notation of 2's complement is 1111 1111.

#### 07. Ans: (d)

**Sol:** The race hazard problem does not occur in combinational circuits.

The output of a combinational circuit depends upon present inputs only.

Statement-I is false but Statement-II is true.

#### 08. Ans: (b)

**Sol:** A de-multiplexer can be used as a decoder. A decoder with enable input acts as a demultiplexer, while using Enable input as a data input line. De-multiplexer is realized using AND gates.

#### 09. Ans: (b)

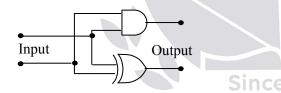

Sol: Half Adder

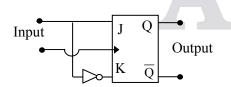

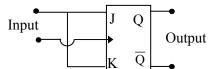

#### **D-Flipflop**

**T-Flipflop**

#### **Exclusive - OR**

#### 10. Ans: (b)

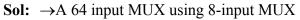

$\rightarrow$  A 6-variable function can be implemented using 6-input MUX.

#### 11. Ans: 195

Sol: In a 16 bit parallel binary adder, the carry has to propagate 15 stages plus the maximum of time taken for producing sum and carry worst case Delay,  $T = 15 \times 12 + 15$ T = 180 + 15T = 195ns.

I = 195ns.

#### 12. Ans: (b)

**Sol:** Any Boolean function can be realized by using a suitable multiplexer.

A multiplexer can be realized using NAND and NOR gates, which are universal gates.

Both statements are correct but statement-II is not a correct explanation for statement-I.

#### **Conventional Practice Solutions**

01. Sol:

#### Truth table:

ACE

If different logic gates are used then minimum number of gates required is 3

|      | ACE                      |

|------|--------------------------|

| 3-2K | Engineering Publications |

Digital & Microprocessors

02.

Sol:

(a) Ex - 3 to 2421 code converter

| Dec no. | Ex-3 Code         | 2 4 2 1 code                                                |

|---------|-------------------|-------------------------------------------------------------|

|         | $E_3 E_2 E_1 E_0$ | Y <sub>3</sub> Y <sub>2</sub> Y <sub>1</sub> Y <sub>0</sub> |

| 0       | 0 0 1 1           | 0 0 0 0                                                     |

| 1       | 0 1 0 0           | 0 0 0 1                                                     |

| 2       | 0 1 0 1           | 0 0 1 0                                                     |

| 3       | 0 1 1 0           | 0 0 1 1                                                     |

| 4       | 0 1 1 1           | 0 1 0 0                                                     |

| 5       | 1 0 0 0           | 1 0 1 1                                                     |

| 6       | 1 0 0 1           | 1 1 0 0                                                     |

| 7       | 1 0 1 0           | 1 1 0 1                                                     |

| 8       | 1 0 1 1           | 1 1 1 0                                                     |

| 9       | 1 1 0 0           | 1 1 1 1                                                     |

|         | DIA               |                                                             |

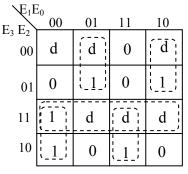

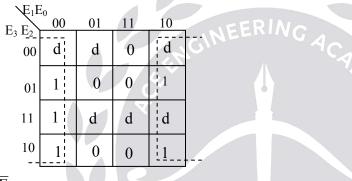

#### K map for Y<sub>3</sub>

|                 | ∖E1E            | Eo             | 4. |    |            |  |

|-----------------|-----------------|----------------|----|----|------------|--|

|                 | · · · · ·       | 00             | 01 | 11 | 10         |  |

|                 | $E_3 E_2$<br>00 | d              | d  | 0  | d          |  |

|                 | 01              | 0              | 0  | 0  | 0          |  |

|                 | 11              | $\overline{1}$ | d  | d  | d          |  |

|                 | 10              | 1              | 1  | _1 | <u>1</u> , |  |

| $Y_{3} = E_{3}$ |                 |                |    |    |            |  |

| \€1E      | 7. |    |                                   |      |

|-----------|----|----|-----------------------------------|------|

| $E_3 E_2$ | 00 | 01 | 11                                | 10   |

| 00        | d  | d  | 0                                 | d    |

| 01        | 0  | 0  | $\begin{bmatrix} 1 \end{bmatrix}$ | 0    |

| 11        | 1  | d  |                                   | dì ) |

| 10        | 0  | 1  | 1                                 | 1,   |

ACE Engineering Publications Hyderabad • Delhi • Bhopal • Pune • Bhubaneswar • Lucknow • Patna • Bengaluru • Chennai • Vijayawada • Vizag • Tirupati • Kolkata • Ahmedabad

Since

1995

#### K-Map for Y<sub>1</sub>

ACE

## $$\begin{split} \mathbf{Y}_1 &= \mathbf{E}_3 \mathbf{E}_1 \mathbf{E}_0 + \overline{\mathbf{E}}_3 \overline{\mathbf{E}}_1 \mathbf{E}_0 + \mathbf{E}_3 \mathbf{E}_1 \mathbf{E}_0 + \overline{\mathbf{E}}_3 \mathbf{E}_1 \overline{\mathbf{E}}_0 + \mathbf{E}_3 \mathbf{E}_2 \\ \mathbf{Y}_1 &= \mathbf{E}_3 \mathbf{E}_2 + \mathbf{E}_3 \oplus \mathbf{E}_1 \oplus \mathbf{E}_0 \end{split}$$

#### K-Map for Y<sub>0</sub>

$$\mathbf{Y}_0 = \mathbf{E}_0$$

02.

Sol:

(b) The excess -3 code table

| Dec | BCD Code | Ex-3 Code |  |  |

|-----|----------|-----------|--|--|

| 0   | 0000     | 0011      |  |  |

| 1   | 0001     | 0100      |  |  |

| 2   | 0010     | 0101      |  |  |

| 3   | 0011     | 0110      |  |  |

| 4   | 0100     | 0111      |  |  |

| 5   | 0101     | 1000      |  |  |

| 6   | 0110     | 1001      |  |  |

| 7   | 0111     | 1010      |  |  |

| 8   | 1000     | 1011      |  |  |

| 9   | 1001     | 1 1 0 0   |  |  |

A self complementary code is a code in which the code of a number and code of 9's complement of that number are complementary to each other so from above table eg: if number is 3 its Ex-3 code is 0110. 9's complement of 3 in Ex-3 code is 1001 which is complementary to 0110. Thus Ex-3 code is a self complementary code.

ACE Engineering Publications Hyderabad • Delhi • Bhopal • Pune • Bhubaneswar • Lucknow • Patna • Bengaluru • Chennai • Vijayawada • Vizag • Tirupati • Kolkata • Ahmedabad

03. Sol:

$F_1 = \sum m(4, 5, 7)$

ACE Engineering Publications Hyderabad • Delhi • Bhopal • Pune • Bhubaneswar • Lucknow • Patna • Bengaluru • Chennai • Vijayawada • Vizag • Tirupati • Kolkata • Ahmedabad

| Postal  | Coac | hing | Sol | lutions |

|---------|------|------|-----|---------|

| i Ustai | Guat | ning | 30  | lucions |

18

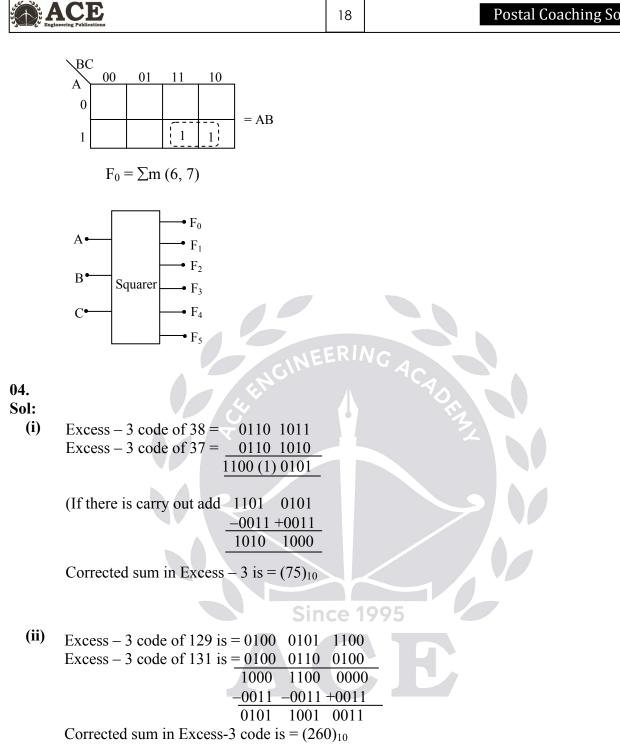

## **Sequential Circuits**

|             | ACE<br>Engineering Publications |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  | 20                             |                   |                             |                     |                   | Pos              | stal Coachi                                                           | ng Sc             | olutions                                   |

|-------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------|-------------------|-----------------------------|---------------------|-------------------|------------------|-----------------------------------------------------------------------|-------------------|--------------------------------------------|

| 06.<br>Sol: | Ans: (b)                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |                                | <b>07.</b>        | Ans                         | <b>: (b</b> )       | )                 |                  |                                                                       |                   |                                            |

| 501:        | CLK                             | Serial in=<br>$B \oplus C \oplus D$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ABCD                                                                             |                                | Sol:              | J                           | K                   | Q                 | $\overline{Q}_n$ | T = (J + C)                                                           | )<br>)            | Q <sub>n+1</sub>                           |

|             | 0                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 0 1 0<br>1 1 0 1                                                               |                                |                   | 0                           | 0                   | 0                 | 1                | $\frac{\left(\mathbf{K} + \overline{\mathbf{Q}}_{n}\right)}{0.1 = 0}$ |                   | ר 0                                        |

|             | 23                              | $\begin{array}{c} 0 \longrightarrow \\ 0 \longrightarrow \\ 0 \longrightarrow \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                             |                                |                   | 0                           | 0<br>1              | 1<br>0            | 0                | 1.0 = 0<br>0.1 = 0                                                    |                   | $\begin{bmatrix} 0 \\ 1 \end{bmatrix} Q_n$ |

|             | 4 5                             | $\begin{array}{c} 0 \longrightarrow \\ 1 \longrightarrow \\ 0 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                             |                                |                   | 0                           | 1 0                 | 1<br>0            | 0                | 1.1 = 1<br>1.1 = 1                                                    |                   | $0 \downarrow 0$<br>1 1                    |

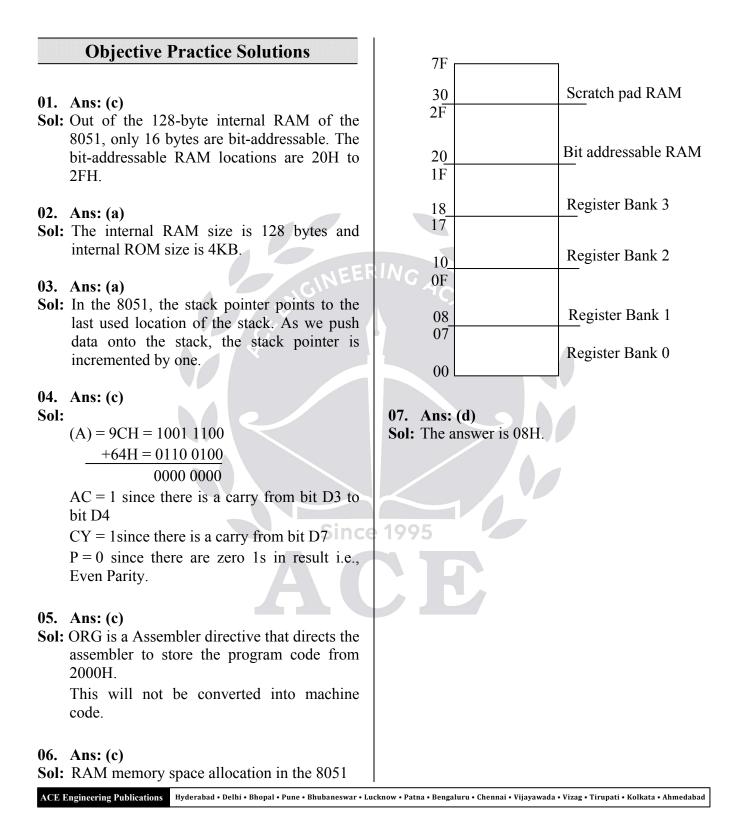

|             | 6<br>7                          | $0 \longrightarrow 1 \longrightarrow 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 1 0 0<br>1 0 1 0                                                               |                                |                   | 1 1                         | 0                   | 1<br>0            | 0<br>1           | 1.0 = 0<br>1.1 = 1                                                    |                   | <u>ו ז ו</u><br>וו                         |