Test-13

Head Office : Sree Sindhi Guru Sangat Sabha Association, # 4-1-1236/1/A, King Koti, Abids, Hyderabad - 500001.

Ph: 040-23234418, 040-23234419, 040-23234420, 040 - 24750437

Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennal | Vijayawada | Vizag | Tirupati | Kukatpaliy | Kolkata | Ahmedabad

### ESE- 2019 (Prelims) - Offline Test Series

**ELECTRONICS & TELECOMMUNICATION ENGINEERING**

#### SUBJECT: CONTROL SYSTEMS, ANALOG ELECTRONICS AND DIGITAL ELECTRONICS & MICRO-PROCESSORS SOLUTIONS

01. Ans: (a)

| Sol: | Number of forward paths $= 4$                |

|------|----------------------------------------------|

|      | $Rx_1x_2x_3x_4C$                             |

|      | $Rx_1x_3x_4C$                                |

|      | $Rx_1x_2x_4C$                                |

|      | $Rx_1x_3x_2x_4C$                             |

|      | Number of loops $= 5$                        |

|      | $x_1x_2x_4x_1$                               |

|      | x <sub>2</sub> x <sub>3</sub> x <sub>2</sub> |

|      | $x_1x_3x_4x_1$                               |

|      | x1x2 x <sub>3</sub> x4x1                     |

|      | $x_1x_3x_2x_4x_1$                            |

|      |                                              |

|      |                                              |

02. Ans: (c)

Sol:

$$S_{K}^{T} = \frac{\partial T}{\partial K} \frac{K}{T}$$

$$= \frac{\partial}{\partial K} \left( \frac{1+3K}{1+2K} \right) \frac{K}{\left( \frac{1+3K}{1+2K} \right)}$$

$$= \left[ \frac{(1+2K)3 - (1+3K)2}{(1+2K)^{2}} \right] \frac{K(1+2K)}{1+3K}$$

$$= \frac{K}{(1+3K)(1+2K)}$$

$$= \frac{K}{1+5K+6K^{2}}$$

Substitute K = 1

$$S_{K}^{T} = \frac{1}{12}$$

03. Ans: (d) Sol:  $c(t) = L^{-1}[R(s)G_2(s)]$   $= L^{-1}\left[\frac{1}{s} \cdot \frac{1}{s+2}\right]$   $= 0.5 (1 - e^{-2t}) u(t)$ 04. Ans: (c) Sol:  $CE = s^4 + 2s^2 + 3 = 0$   $s^4 | 1 2 3$   $s^2 | 1 3$   $s^2 | 1 3$   $s^1 | -8 0$ Given equation is AE,  $\frac{dAE}{ds} = 4s^3 + 4s = 0$ Number of sign changes below the AE = 2

Number of RHP = Number of LHP = 2

Number of  $j\omega P = 0$

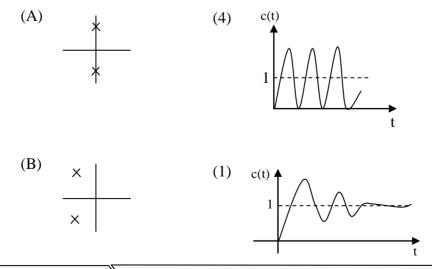

The four poles are located in quadrate as shown below

$$\begin{array}{c|c} \times & \times \\ \hline \\ \times & \times \end{array}$$

05. Ans: (a)

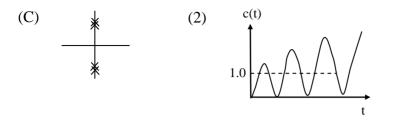

Sol: Location of poles

Unit step response

:3:

06. Ans: (c)

Sol:

$$\frac{V_{o}(s)}{V_{i}(s)} = \frac{\left[\frac{1}{Cs}\right]\left[\frac{1}{Cs}\right]}{R\left[R + \frac{1}{Cs} + \frac{1}{Cs}\right] + \frac{1}{Cs}\left[R + \frac{1}{Cs}\right]}$$

Substitute R = 1Ω, C = 1F

$$\frac{V_{o}(s)}{V_{i}(s)} = \frac{1}{s^{2} + 3s + 1}$$

07. Ans: (c)

Sol:

$$C(s) = TF \times R(s)$$

$R(s) = L[cost] = \frac{s}{s^2 + 1}$

$C(s) = \frac{1}{s^2} \cdot \frac{s}{s^2 + 1} = \frac{1}{s(s^2 + 1)} = \frac{1}{s} + \frac{-s}{s^2 + 1}$

$c(t) = L^{-1}[C(s)] = 1 - cost$

Sol: Noise transfer function

$$\frac{C(s)}{N(s)} = \frac{G_1}{1 - (-2G_1G_2H)}$$

$$= \frac{G_1}{2G_2G_1H + 1}$$

#### **09. Ans:** (b)

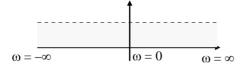

Sol: From option (b)  $\omega = 0.... \angle \phi = -270^{\circ}$  $\omega = \infty.... \angle \phi = -180^{\circ}$

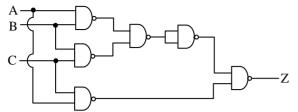

### GATE+PSUs - 2020

Admissions Open From 14th NOV 2018

HYDERABAD -

29<sup>th</sup> April | 06<sup>th</sup> May | 11<sup>th</sup> May 18<sup>th</sup> May | 26<sup>th</sup> May | 02<sup>nd</sup> June 2019

DELHI

11th May 23rd May 2019

### EARLY BIRD OFFER :

Register on or Before 31" December 2018 : 5000/- Off | Register on or Before 31" March 2019 : 3000/- Off

## **TEST YOUR PREP** IN A REAL TEST ENVIRONMENT

# Pre GATE - 2019

Date of Exam : 20<sup>th</sup> January 2019 Last Date to Apply : 31st December 2018

#### **Highlights**:

- Get real-time experience of GATE-2019 test pattern and environment.

- \* Virtual calculator will be enabled.

- \* Post exam learning analytics and All India Rank will be provided.

- \* Post GATE guidance sessions by experts.

- \* Encouraging awards for GATE-2019 toppers.

10. Ans: (b) Sol:  $\left|\frac{\mathbf{k}}{\mathbf{s}^2}\right|_{\omega=10} = 1$  $\frac{\mathbf{k}}{\omega^2} = 1$  $\mathbf{k} = \omega^2 = 10^2$  $\therefore \mathbf{K}_a = \mathbf{k} = 100$

#### 11. Ans: (a)

Sol: The number of loops = 4 Loop gains = 1, 1, 1, -1  $\therefore$  Sum of individual loop gains = 1 + 1 + 1 - 1 = 2

#### 12. Ans: (b)

Sol: PM =180°+

$$\angle \frac{j\omega + 1}{(j\omega)^2 \sqrt{2}} \Big|_{\omega = \omega_{gc}}$$

$\left| \frac{j\omega_{gc} + 1}{(j\omega_{gc})^2 \sqrt{2}} \right| = \frac{\sqrt{\omega_{gc}^2 + 1}}{\omega_{gc}^2 \sqrt{2}} = 1$

$\omega_{gc} = 1 \text{ rad/sec}$

$\therefore PM = 180° + \tan^{-1}\omega_{gc} - 180°$

PM = 45°

#### 13. Ans: (c)

Sol: For region 1 N = -1For region 2 N = -2For region 3 N = 0Given, P = 0, Z = 0 $\therefore N = P - Z = 0$ Only if (-1, j0) lies in region (3) N is zero

#### 14. Ans: (a)

- **Sol:** A derivative controller

- $\rightarrow$  improves the stability of the system

- $\rightarrow$  improves phase margin

- $\rightarrow$  decreases over shoot

- $\rightarrow$  decreases settling time

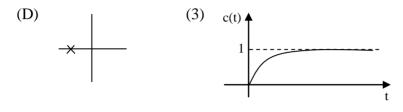

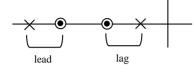

#### 15. Ans: (b)

Sol: Transfer function of lag-lead compensator is

$$G_{c}(s) = \frac{(s + Z_{1})(s + Z_{2})}{(s + P_{1})(s + P_{2})} \text{ where } P_{1} < Z_{1} < Z_{2} < P_{2}$$

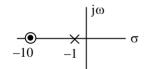

Pole zero plot of lag-lead compensator

16. Ans: (b)

Sol:

$$k_{p} = \underset{s \to 0}{\text{Lt }} G(s) = \infty$$

$$k_{v} = \underset{s \to 0}{\text{Lt }} \underset{s \to 0}{s} G(s) = \infty$$

$$k_{a} = \underset{s \to 0}{\text{Lt }} \underset{s^{2}}{s^{2}} G(s) = 10$$

Error due to  $1 + t + \frac{t^{2}}{2} = \frac{1}{1 + k_{p}} + \frac{1}{k_{v}} + \frac{1}{k_{a}} = 0.1$

17. Ans: (b)

Let  $G_{c}(s) = \frac{1 + s/10}{1 + s/1}$ Sol:

Pole zero plot of lag compensator

18. Ans: (c)

Sol: Given positive feedback system : Characteristic equation 1 - G(s)H(s) = 0 $1 - \frac{k}{s-6} = 0$ s - 6 - k = 0s - (k + 6) = 0k + 6 < 0k < -6

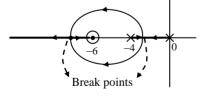

Sol:

$$G(s) H(s) = \frac{k}{s(s+1)(s+2)}$$

$CE = 1 + G(s)H(s) = 0$

$s(s+1)(s+2) + k = 0$

$s^3 + 3s^2 + 2s + k = 0$

Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Vizag | Tirupati | Kukatpally | Kolkata | Ahmedabad ACE Engineering Academy

$\therefore$  The value of k at point A = 6

#### 20. Ans: (b)

Sol: Every branch of the RLD starts at a pole (k = 0), and terminates at a zero ( $k = \infty$ ) of the OLTF G(s)H(s).

:7:

On the real axis to the right side of any section, if the sum of total no. of open loop poles and zeros are odd, RLD exists in that section.

Sol:

$$\frac{C(s)}{R(s)} = T(s) = \frac{(s+2)e^{-s}}{(s^{2}+4)}$$

Impulse response = L<sup>-1</sup> (T(s))

$$T(s) = \frac{se^{-s}}{s^{2}+4} + \frac{2e^{-s}}{s^{2}+4}$$

IR = L<sup>-1</sup> (T(s))

$$IR = L^{-1} \left[\frac{se^{-s}}{s^{2}+4}\right] + L^{-1} \left[\frac{2e^{-s}}{s^{2}+4}\right]$$

IR = cos 2(t-1) + sin 2(t-1)

22. Ans: (b)

Sol:

- 23. Ans: (c)

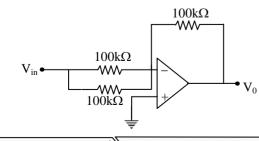

- **Sol:** When the switch (S/W) is on:

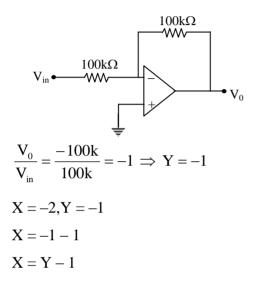

$$V_0 = -\frac{R_f}{R} = -\frac{100 \,k}{100 \,k //100 \,k} \times V_{in}$$

$$\frac{V_0}{V_{in}} = -2 \implies X = -2$$

When the switch is OFF:

#### 24. Ans: (c)

- Sol: If the emitter bypass capacitor in a common emitter amplifier is removed,

- i) The input resistance of the amplifier will be increased

- ii) The voltage gain of the amplifier will be decreased.

#### 25. Ans: (c)

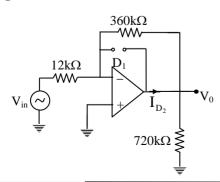

Sol: During positive half-cycle of input voltage,

$\begin{array}{l} D_1 \rightarrow ON \\ D_2 \rightarrow OFF \quad \Rightarrow I_{D_2} = 0 \end{array}$

During negative half-cycle of input voltage,

$\begin{array}{c} D_1 \rightarrow OFF \\ D_2 \rightarrow ON \end{array}$

$V_{_0}=-30V_{_{in}}$  and  $V_{_{in}}=-2\sin\omega t$

$\therefore$  V<sub>0</sub> = 60 sin  $\omega$ t

The output voltage waveforms are shown below

$$I_{D2} = \frac{V_0}{720k} + \frac{V_0}{360k} = \frac{V_0}{240k} = 0.25 \sin \omega t \text{ mA when } V_{in} < 0$$

RMS value of  $I_{D2} = \frac{0.25}{2} = 0.125 \text{ mA}$

- 26. Ans: (c)

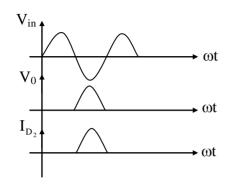

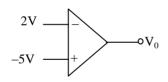

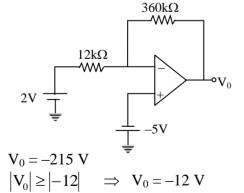

- **Sol:** Open loop configuration:

$$V_0 = (-5 - 2) A_0 \Rightarrow -Ve$$

∴  $D_1 \rightarrow OFF; D_2 \text{ is ON}$

#### 27. Ans: (c)

Sol:

$\begin{array}{ll} (i) & \mbox{For cut-off region:} \\ & V_{SG} < |V_{tp}| \\ & V_S - V_G < 0.5 \end{array}$

ACE Engineering Academy Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Vizag | Tirupati | Kukatpally | Kolkata | Ahmedabad

:9:

$$-V_G < 0.5 - 3$$

$V_G > 2.5V$

- $\begin{array}{ll} \mbox{(ii)} & \mbox{For triode region:} \\ & V_{SD} < V_{SG} |V_{tp}| \\ & V_S V_D < V_S V_G 0.5 \\ & 3 1 < 3 V_G 0.5 \\ & V_G < 0.5 V \end{array}$

- (iii) For saturation region:  $V_{SD} \ge V_{SG} - |V_{tp}|$   $3 - 1 \ge 3 - V_G - 0.5$   $V_G \ge 0.5V$

- 28. Ans: (b)

Sol:

$$-V_{D2} + V_{D1} + V = 0$$

$V = V_{D2} - V_{D1} = 50 \text{mV}$

$10 \text{mV} = I_1 + I_2$

$\frac{I_2}{I_1} = \frac{I_s e^{\frac{V_{D2}}{V_T}}}{I_s e^{\frac{V_{D2}}{V_T}}} = e^{\frac{V_{D2} - V_{D1}}{V_T}}$

$\frac{I_2}{I_1} = e^{\frac{50 \text{mV}}{25 \text{mV}}} = e^2$

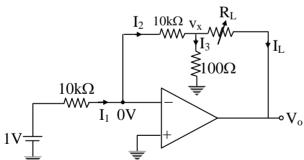

29. Ans: (c) Sol:

$$I_{1} = \frac{1}{10k} = 0.1mA$$

$$I_{2} = I_{1} = 0.1mA$$

$$(10k I_{2}) + (100 I_{3}) = 0$$

$$I_{3} = \frac{-10k \times 0.1m}{100} = -10mA$$

$$V_{x} = -100 \times 10m$$

$$V_{x} = -1V;$$

$$\begin{split} I_{L} &= I_{2} - I_{3} \\ &= 10.1 \text{mA} \\ V_{0} &= V_{x} - I_{L} R_{L} \\ V_{0} &= -1 - 10.1 \text{m } R_{L} \\ \text{When } R_{L} &= 100 \Omega \\ \rightarrow \quad V_{0\text{max}} &= -1 - (10.1 \times 10^{-3} \times 100) \\ &= -2.01 \text{V} \\ \text{When } R_{L} &= 1 \text{k} \Omega \\ \rightarrow \quad V_{0\text{min}} &= -1 - (10.1 \times 10^{-3} \times 10^{3}) \\ &= -11.1 \text{W} \end{split}$$

$$-11.1 \text{ v}$$

$-11.1 \text{ V} < \text{V}_0 < -2.01 \text{ V}$

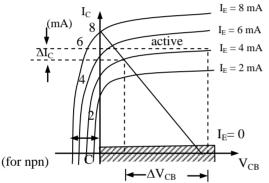

- **30.** Ans: (c)

- Sol: Output Characteristics: I<sub>C</sub> vs V<sub>CB</sub>|I<sub>E</sub>

#### **Saturation Region:**

- Saturation region is the region left side to  $V_{CB} = 0$  line.

- In saturation region, emitter and collector junction are in forward bias.

- In saturation region, collector current increases exponentially.

- It can be used as ON switch in saturation region.

#### 31. Ans: (c)

**Sol:** The emitter capacitance (C<sub>E</sub>) is increases the gain  $\left(\frac{V_0}{V_s}\right)$  and input resistance (R<sub>in</sub>) decreases

for AC signals.

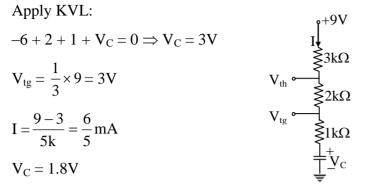

- 32. Ans: (c)

- Sol: A 555 timer change the state when threshold voltage,  $V_{th}$  is just greater than  $\frac{2V_{cc}}{3}$  volts and

trigger voltage,  $V_{tg}$  is just below the  $\frac{V_{CC}}{3}$  volts.

$$V_{th} = \frac{2}{3} \times 9 = 6V$$

$$I = \frac{9-6}{3k} = 1mA$$

ACE Engineering Academy Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Vizag | Tirupati | Kukatpally | Kolkata | Ahmedabad

:11:

Therefore, the range of the voltage across the capacitor,  $V_c$  is 1.8V to 3V

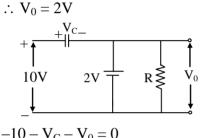

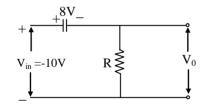

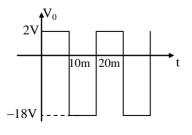

#### 33. Ans: (c)

**Sol:** When  $V_i = +10V$ , diode is forward biased

$$10 - V_C - 2 = 0$$

$V_C = +8V$

When  $V_{in} = -10V$ , diode is reverse biased.

$$-10 - 8 = \mathbf{V}_0 \Longrightarrow \mathbf{V}_0 = -18\mathbf{V}$$

#### The output wave form:

Average output voltage,  $2 \times 10m - 18 \times 10m$

$$V_0 = \frac{2 \times 10m - 18 \times 10m}{20m} = -8V$$

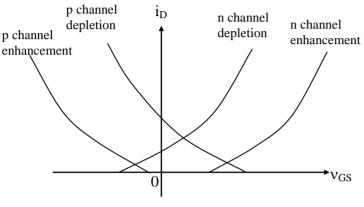

**34. Ans:** (c) **Sol:** In E-MOS

In E-MOSFET  $V_{GS} = 0$  then  $I_D = 0$ If  $+V_{GS}$  increases then ' $I_D$ ' also Increases

- 35. Ans: (c)

- Sol: The phase of loop gain should be zero. So statement(ii) is wrong.

- 36. Ans: (c)

- Sol:

∴ P- III, Q-II, R-IV, S-I

- 37. Ans: (c)

- Sol: Overall voltage gain = product of individual voltage gains =  $25 \times 10 \times 4 = 1000$ Overall gain in dB =  $20 \log_{10} 1000 = 60$ dB

- **38.** Ans: (d)

Sol:

$$I_{D} = \frac{2.5 - 1.8}{R}$$

$0.5 \text{mA} = \frac{0.7 \text{V}}{R}$

$R = \frac{0.7}{0.5 \text{m}} = 1.4 \text{k}\Omega$

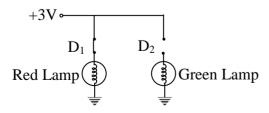

- **39. Ans:** (b)

- **Sol:** For  $V_i = 3V$ ,  $D_1$  is in forward bias,  $D_2$  is in reverse bias

∴ RED lamp gets ON GREEN lamp gets OFF

ACE Engineering Academy Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Vizag | Tirupati | Kukatpally | Kolkata | Ahmedabad

:13:

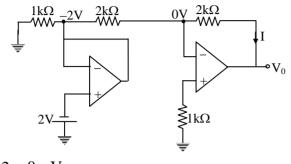

#### 40. Ans: (c)

**Sol:** By open-loop comparator,  $D_1$  is ON and  $D_2$  is OFF

$$\frac{0+2}{2k} + \frac{0-V_0}{2k} =$$

$$V_0 = 2V$$

The current through resistor,  $I = \frac{-2}{2k} = -1mA$

0

41. Ans: (a)

Sol:

$$f'_{L} = \frac{f_{L}}{\sqrt{2^{\frac{1}{n}} - 1}}$$

$f'_{L} = \frac{20}{\sqrt{2^{1/3} - 1}} = 39.229 \text{ Hz}$

- 42. Ans: (a)

- Sol: 1. The Leakage current  $I_{CB0}$  doubles for every  $10^{0}$ C rise in temperature.

- 2. Base emitter voltage  $V_{BE}$  decreases by 2.5 mV for every 1°C rise in temperature.

- 3. As temperature increases  $I_c$  increases so power dissipation at the junction increases.

#### 43. Ans: (a)

Sol:  $I_c = \beta I_B + I_{CE0}$ =  $\beta I_B + (\beta+1) I_{CB0}$ = 100 (10µA) + 101 (100 nA) = 1 mA + 0.0101mA = 1.0101 mA

44. Ans: (c)

Sol:  $V_{3k} = 15.\frac{3}{2+3}$ = 9V  $V_{3k} < Vz$  Hence zener diode is O.C Hence  $I_L = \frac{15}{2K+3K} = 3mA$

#### 45. Ans: (b)

Sol: 1. Crystal oscillators were used whenever the greater stability of oscillations are required

:15:

- 2. RC oscillators are low frequency oscillators

- 3. LC oscillators are high frequency oscillators

- 4. In Hartley oscillator mutual inductance between two feedback inductors will effects the frequency of oscillation

#### 46. Ans: (b)

**Sol:** If  $V_{in} > V_{out}$  set next bit

If  $V_{in} < V_{out}$  set bit is going to reset and will set next bit Here given that, Analog input  $(V_{in}) = 6.2V$ Digital output is greater than 6.2V so reset the last set bit and set the next bit. Given digital input is equal to  $110\underline{1}0000$  $\therefore$  next value of SAR is 11001000

#### 47. Ans: (c)

Sol: The maximum number of Boolean functions with

'n' variables =  $2^{2^n}$ For '5' variables =  $2^{2^5}$ =  $2^{3^2}$ = 4294967296

#### 48. Ans: (b)

- **Sol:** 1) Without using any additional logic gates, we cannot implement all Boolean functions using decoder.

- 2) Any function can be implemented using suitable MUX.

- 3) MUX is producing only one output, it cannot be used for multiple output function.

#### 49. Ans: (b)

**Sol:**  $f(A,B,C,D) = \prod M(0,4,5,7,12,15)$

| $=\Sigma_{1}$                                     | m (1,2,        | 3,6,8,9         | 9,10,11 | ,13,14) |

|---------------------------------------------------|----------------|-----------------|---------|---------|

| A B                                               | I <sub>0</sub> | $I_1$           | $I_2$   | $I_3$   |

| $S_1$ $S_0$                                       | 0.0            | 01              | 10      | 11      |

| $\overline{\mathrm{C}}\overline{\mathrm{D}}$ (00) | 0              | 4               | 8       | 12      |

| $\overline{C}D(01)$                               |                | 5               | 9       | 13      |

| $\overline{CD}$ (10)                              | (2)            | 6               | 10      | (14)    |

| CD (11)                                           | 3              | 7               | (1)     | 15      |

|                                                   | C+D            | $C\overline{D}$ | 1       | C⊕D     |

| $I_0 = C + D$                                     |                |                 |         |         |

| $I_1 = C\overline{D}$                             |                |                 |         |         |

| $I_2 = 1$                                         |                |                 |         |         |

| $I_3 = C \oplus D$                                |                |                 |         |         |

ACE Engineering Academy

## Launching Spark Batches for ESE / GATE - 2020 from Mid May 2019

Admissions from January 1st, 2019

## Launching Regular Batches for ESE / GATE - 2020

## from Mid May 2019

Admissions from January 1st, 2019

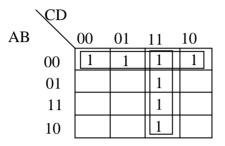

50. Ans: (d)

**Sol:**  $f(A, B, C, D) = \overline{A} \overline{B} \overline{C} \overline{D} + \overline{A} \overline{B} \overline{C} D + \overline{A} \overline{B} \overline{C} \overline{D} + \overline{A} \overline{B} \overline{C} D + \overline$

:17:

$=\Sigma m(0, 1, 2, 3, 7, 11, 15)$

The simplified form of  $f(A, B, C, D) = \overline{A} \overline{B} + CD$

- 51. Ans: (c)

- **Sol:**  $(63)_{16} + (37)_{16} = (9A)_{16}$

$\therefore$  Y = 9A H

- 52. Ans: (b)

- **Sol:** It is up counter

All the flip flops are clearing when  $Q_2 Q_1 = 11$

$$\begin{pmatrix} 0 & 0 & 0 \\ 0 & 0 & 1 \\ 0 & 1 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 0 \Rightarrow 0 & 0 & 0 \\ \end{pmatrix}$$

As it is asynchronous counter 100 state is overwriting with 000.

So it is counting only 4 states

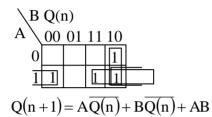

| 53. | Ans: | (a) |

|-----|------|-----|

|     |      | ()  |

Sol:

| А | В | Q(n+1)            |

|---|---|-------------------|

| 0 | 0 | 0                 |

| 0 | 1 | $\overline{Q(n)}$ |

| 1 | 0 | $\overline{Q(n)}$ |

| 1 | 1 | 1                 |

|   | Α | В | Q(n) | Q(n+1) |

|---|---|---|------|--------|

| 0 | 0 | 0 | 0    | 0      |

| 1 | 0 | 0 | 1    | 0      |

| 2 | 0 | 1 | 0    | 1      |

| 3 | 0 | 1 | 1    | 0      |

| 4 | 1 | 0 | 0    | 1      |

| 5 | 1 | 0 | 1    | 0      |

| 6 | 1 | 1 | 0    | 1      |

| 7 | 1 | 1 | 1    | 1      |

54. Ans: (d)

The 10's complement of decimal number = 9's complement + 1 Sol:

> 9999.99999 (-)6091.20100 9's complement  $\Rightarrow$  3908.79899 (+) \_\_\_\_\_1 10's complement  $\Rightarrow$  3908.79900

55. Ans: (c) Sol:

|                     |    | Ā  | -         |    | А                     |

|---------------------|----|----|-----------|----|-----------------------|

| $\langle D \rangle$ | E  |    |           |    | \_DE                  |

| BC \                | 00 | 01 | 11        | 10 | BC <u>00 01 11 10</u> |

| 00                  |    | 1  |           |    | 00 1                  |

| 01                  | 1  | 1  | 1         | 1  | 01 1 1 1 1            |

| 11                  | 1  | 1  | 1         | 1  | 11 1 1 1 1            |

| 10                  | 1  | 1  | <u>`1</u> | 1  | 10 1 1 1 1            |

Total number of minterms = 26

56. Ans: (c) f = AB + BC + ACSol:  $=\overline{AB + BC + AC}$  $=\overline{AB}.\overline{BC}.\overline{AC}$  $=\overline{AB}.\overline{BC}.\overline{AC}$

The function requires minimum 6 number of NAND gates to be realized.

:19:

- 57. Ans: (c)

- **Sol:** ECL logic family has

- (1) Very high switching speed

- (2) High power dissipation

- (3)

| Voltage Level | State | Boolean<br>Logic |

|---------------|-------|------------------|

| -0.8V         | HIGH  | Logic '1'        |

| -1.8V         | LOW   | Logic '0'        |

ECL logic family uses negative voltage levels for both logic 1 and 0.

(4) Fan-out capability is high

#### 58. Ans: (d)

Sol: In fourth generation embedded system, the system on chip(SOC) is used.

#### 59. Ans: (a)

**Sol:** Given that rotor is at "C" initially

| Input (xy) | <b>Rotor Position</b> |

|------------|-----------------------|

|            | С                     |

| 00         | С                     |

| 01         | D                     |

| 10         | С                     |

| 10         | В                     |

| 11         | В                     |

| 00         | В                     |

| 10         | А                     |

| 11         | А                     |

Therefore position of rotor after the inputs in given sequence is 'A'.

#### 60. Ans: (c)

- **Sol:** 1) Registers are made of edge triggered flops where as latches are made from level triggered flip flops.

- 2) Latch employs cross coupled feed back connections.

- 3) Noise immunity is the amount of noise which can be applied at the input of the gate without causing the gate to change state.

- 4) Propagation delay is the time required for a gate to change its state.

- 61. Ans: (c)

- **Sol:**  $S_1$ : Flash ADC is fastest ADC.

- S<sub>2</sub>: The most widely used ADC in multimeter is Successive approximation ADC.

- $S_3$ : The conversion time for Successive approximation ADC depends only on number of output bits. It doesn't depends on applied input voltage.

- S<sub>4</sub>: In dual slope ADC integrator is used.

#### 62. Ans: (d)

**Sol:** CMOS logic family is having the given two merits, Hence it became familiar in most of the real time applications today.

#### 63. Ans: (d)

- Sol: MVI  $A, 06_H; [A] = 06H = 00000110_2$ RLC ;  $[A] = 00001100_2 = 0CH$ MOV B, A ;  $[B] = 0CH = 00001100_2$ RLC ;  $[A] = 00011000_2$ RLC ;  $[A] = 00110000_2 = 30H$ ADD B  $[A] = [A]+[B] = 30H + 0CH = 3C_H$ HLT

- 64. Ans: (c)

- **Sol:** The 8051 requires an external oscillator circuit. The oscillator circuit usually runs around 12MHz. Each machine cycle in the 8051 is 12 clock cycles, giving an effective cycle rate at 1MHz to 3.33 MHz.

One Machine cycle has 6 states. One state is 2T-states.

$\therefore$  One machine cycle is 12T-states.

#### 65. Ans: (c)

**Sol:** Interrupt vector table on 8086 is a vector that consists of 256 total interrupts placed at first 1kB of memory from 0000H to 03FFH.

#### 66. Ans: (b)

**Sol:** Segmentation is a technique for allocating memory in chunks of varying and meaningful sizes instead of one arbitray page size i.e., segmentation splits the memory into unequal units. Therefore statement (3) is wrong

#### 67. Ans: (b)

Sol:

- (A) XTHL: Exchanges the contents of H and L registers with top of stack. It takes 5 machine cycles = 16T states

- (B) PUSH B: The contents of the register pair designated in the operand are copied onto the stack in the following sequence. The stack pointer register is decremented and the contents of the high order register (B) are copied into the location.

The stack pointer register is decremented again and the contents of the low-order register (C) are copied to that location.

3 Machine cycles = 12 T-states

- (C) HLT: Halt and enter into wait state It takes 5 T-states.

- (D) XCHG: The contents of the register H are exchanged with the contents of register D, and the contents of register L are exchanged with the contents of register E. 1-Fetch machine cycle = 4T states

:21:

#### 68. Ans: (d)

Sol: AAD stands for "ASCII Adjust before Division". This instruction adjusts two unpacked BCD digits (Least significant digit in AL register and the most significant digit in AH register) so that a division operation performed on the result will yield a correct unpacked BCD value. AAD instruction useful only when it precedes a DIV instruction.

69. Ans: (d)

**Sol: Statement (I):** If impulse is applied to second order system, it oscillates with its natural frequency, only if the poles lie on the imaginary axis.

Statement (II): Impulse consists of infinite frequency components, whose spectrum is shown in figure below.

#### 70. Ans: (d)

Sol:

Given C.E is  $4s^2 + 6s + 1 = 0 \rightarrow (1)$ Standard form of characteristic equation is,  $s^2 + 2\zeta \omega_n s + \omega_n^2 = 0 \rightarrow (2)$ Compare eq(1) and (2),then we get  $\omega_n = 0.5$  rad/sec and  $\zeta = 1.5$ System is over damped ( $\zeta > 1$ )

#### 71. Ans: (a)

Sol:

$$CLTF = \frac{G(s)}{1 + G(s)H(s)}$$

$CE = 1 + G(s)H(s) = 0$

For system to be stable roots (zeros) of characteristic equation must lie on left half of s-plane.

Poles of CLTF is nothing but zeros of characteristic equation.

#### 72. Ans: (b)

Sol: Both the statements are correct but statement (II) is not the correct explanation for Statement (I).

#### 73. Ans: (a)

**Sol:** In a BJT, the majority of the stored charge is in the form of minority carriers which are diffusing across the device in forward operation. Whereas in FET current is only due to majority carriers. So there is no minority stored charge in FET. Both the statements are true and statement (II) is correct explanation for statement (II).

#### 74. Ans: (d)

**Sol:** DRAM stores charge in the form of charge. Each memory cell in DRAM is made of transistor and capacitor. The data will be stored in capacitor. So, DRAM must be refreshed regularly since capacitor loose charge due to leakage.

SRAM is faster than DRAM since it doesn't have refreshing circuit.

#### 75. Ans: (c)

Sol: Statement (I) is true because  $(0100\ 0111\ 1000\ 1001)_2$ , 16 bit can be stored as  $(4789)_{16}$  in hexadecimal.

Statement (II) is False, since four times of binary number is 8 not 16.

# **CONGRATULATIONS TO OUR** ESE - 2018 TOP RANKERS

AIR

SHADAB ANAMAD

EF.

AIR

CHIRAG JHA

AMIT KUMAR

VUAYA NANDAN CE

EAT

EE

CE

AIR

AMAN JAIN ME

SRUAN VARMA EE

KARTHIK KOTTURU

SHANAVAS CP

TENCH

EE

ROHIT KUMAR CE

SOUVIK DEB ROY

EE.

AIR

MAYUR PATIL ME

ANKIT GARG

AIR

BARENDRA KUMAR

www.aceenggacademy.com

AIF

п

AIR

AIR

BURYASH GAUTAM

ROOPESH MITTAL CE

JAPJIT SINGH

CHIRAG

PRATHAMESH