Head Office : Sree Sindhi Guru Sangat Sabha Association, # 4-1-1236/1/A, King Koti, Abids, Hyderabad - 500001.

Ph: 040-23234418, 040-23234419, 040-23234420, 040 - 24750437

Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennal | Vijayawada | Vizag | Tirupati | Kukatpaliy | Kolkata | Ahmedabad

#### 07. Ans: (a)

**Sol:** The F's complement of hexadecimal number C091.20F30

F's complement

$$\Rightarrow$$

(-)

FFFF . FFFFF

C091 . 20F30

FFF . FFFFF

C091 . 20F30

FFF . FFFFF

#### F30 OCF

#### 08. Ans: (a)

**Sol:** It is mod 12 counter. After 300 clock cycles

300% 12 = 0

So, the state after 300 clock cycles is initial state only.

So,  $Q_3 Q_2 Q_1 Q_0$  state after 300 clock cycles is 0000.

#### **09. Ans:** (d)

Sol: A synchronous counter state changes in one Flipflop delay, if it is changing from one state to another state. The propagation delay is independent of number of bits.

$\therefore$  The maximum time required is 10ns.

#### **10.** Ans: (b)

**Sol:** It is a ring counter . So  $D_3=Q_0$ ,  $D_2=Q_3$ ,  $D_1$  $= Q_2, D_0 = Q_1$

$$\begin{array}{c} Q_3 Q_2 Q_1 Q_0 \\ \hline 0 & 1 & 0 & 1 \\ 1 & 0 & 1 & 0 \\ 1 & 0 & 1 & 0 \end{array}$$

The modulus of counter is '2'

#### 11. Ans: (c)

**Sol:** The size of the ROM =  $128 \times 8 = 2^7 \times 8$  $\Rightarrow$ The total number of bits need not to be programmed =  $[2^7 \times 8] - [2^6 \times 6]$  $=2^{6}[(2\times 8)-6]$  $= 64 \times 10$ = 640

#### : 2 : Electronics & Telecommunication Engineering

#### 12. Ans: (d)

Sol: The capacity of PLA is specified by the number of inputs, number of product terms and number of outputs.

#### 13. Ans: (c)

Sol: MOS logic offers low power consumption. Because of the low voltage requirement, it is highly suitable for battery operated systems.

> MOS logic has highest packing density and high fan-out

#### 14. Ans: (b) Sol:

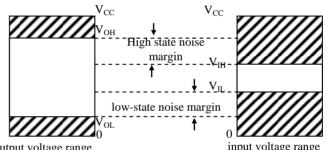

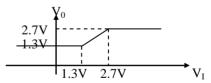

output voltage range

input voltage range

From the signals for evaluating noise margin shown above,

$V_{OH} > V_{IH}$  $V_{IL} > V_{OL}$  $V_{OH} > V_{OL}$  $V_{IH} > V_{IL}$  $\therefore$  option (b) is incorrect

#### 15. Ans: (c)

Sol: For hard real-time systems, no deadline misses are tolerated. For soft real-time systems, it is acceptable for tasks to miss deadlines occasionally and tasks not finished by their deadlines are still completed, albeit with reduced values. Firm real-time systems also allow occasional deadline misses.

ACE Engineering Academy Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Vizag | Tirupati | Kolkata | Ahmedabad

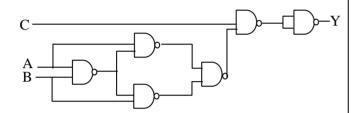

- 16. Ans: (d) Sol:  $Z = \overline{C} \overline{D} \overline{A} \overline{B} + \overline{C} D (\overline{A}B + AB) + CDAB$  $= \overline{A} \overline{B} \overline{C} \overline{D} + \overline{A} \overline{B} \overline{C} D + AB \overline{C} D + ABCD$  $= \sum m(0,5,13,15)$

- 17. Ans: (b)

- **Sol:** (A)  $Y = A\overline{B}C + \overline{A}BC = (A \oplus B)C$

For Y operation 6 NAND gates are required

(B)  $Y = \overline{AB} + AB + \overline{C} = 1 + \overline{C} = 1$ No need of NAND gate (C)  $Y = A\overline{B}[1 + C] + \overline{AB}$

$$Y = A \oplus B$$

4 NAND gates are required.

#### 18. Ans: (a)

- Sol: AB + BC + AC is a self dual function AB + BC + AC is carry output of full adder AB + BC + AC is resulting output 1 when number of 1's are more Full subtractor borrow expression is =  $\overline{AB} + BC + \overline{AC}$

- **19.** Ans: (c)

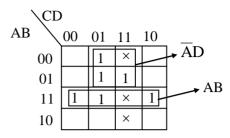

- Sol:  $f(A,B,C,D) = \Sigma m(1, 5, 7, 12, 13, 14) + d(3, 11, 15)$

$f(A, B, C, D) = AB + \overline{A}D$ For the input 0011, f = (0.0) + (1.1) = 1For the input 1011, f = (1.0) + (0.1) = 0

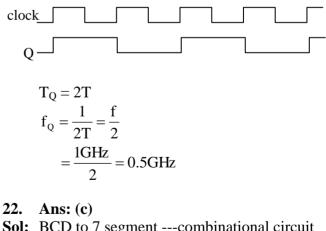

#### 21. Ans: (c)

**Sol:** The circuit is SR flip flop with  $S = \overline{Q}$  and R = Q.

So the output Q is complementing at every clock cycle

Sol: BCD to 7 segment ---combinational circuit 4 to 1 multiplexer ---- combinational circuit 4 bit shift register --- sequential circuit BCD counter ---- sequential circuit

ACE Engineering Academy

#### 23. Ans: (c)

**Sol**: Synchronous counter will provide clock at a time to all flip flops. Hence it provides least delay compared to other counters.

#### 24. Ans: (b)

- Sol: (a) Correct statement

- $R_1$  = Resolution of 10 bit digital ramp ADC

$$=\frac{V_{ref}}{2^{10}-1}$$

$R_2$  = Resolution of 8 bit digital ramp ADC

$$=\frac{V_{ref}}{2^8-1}$$

$$R_1 < R_2$$

$R_1$  has better resolution than  $R_2$

- (b) Conversion time of SAR = nT That means independent of input voltage, SAR conversion time is always depends on number of bits only

- (c) A flash ADC not contains a DAC is also right statement.

- (d) VCO is the main component of a voltage to frequency ADC. This also right statement.

25. Ans: (c)

**Sol:** Resolution =  $\frac{100 - 0}{2^6 - 1} = \frac{100}{63}$  rpm

| MVI B,    | 00H;                                    | [B] = 00H                                    |

|-----------|-----------------------------------------|----------------------------------------------|

| MVI C,    | 00H;                                    | [C] = 00H                                    |

| OP: DCR C | ;                                       | [C] = FFH                                    |

| JNZ LOO   | OP ; Z-fla                              | g = 1 so again loop executes                 |

|           | till [0                                 | C] = 00H, i.e 256 times                      |

| DCR B     | ; [B] =                                 | = FFH                                        |

| JNZ LOO   | OP ; zero                               | flag = 1 so again loop executes              |

|           | MVI C,<br>DP: DCR C<br>JNZ LOO<br>DCR B | JNZ LOOP ; Z-fla<br>till [0<br>DCR B ; [B] = |

The number of steps required for 50 speed

is

$$=\frac{50}{100/63} \approx 32_{10} = 100000_2$$

#### 26. Ans: (b)

**Sol:** Resolution =

$$0.01\% = \frac{0.01}{100}$$

$$=\frac{1}{10,000}=\frac{1}{2^{n}}$$

Minimum number of bits = 14

#### 27. Ans: (b)

Sol: A dual slope ADC integrates an unknown input voltage ( $V_{in}$ ) for a fixed amount of time ( $T_{int}$ ), then de-integrates ( $T_{de-int}$ ) using a known reference voltage ( $V_{REF}$ ) for a variable amount of time.

$$T_{int}$$

is fixed

$T_{de-int} \alpha \frac{V_{in}}{V_{REF}}$

Any error introduced by a component value during the integrate cycle will be cancelled out during the de-integrate phase.

$\therefore$  De-integration time period is variable and depends on number of pulses counted during 1<sup>st</sup> integration.

ACE Engineering Academy 💦 Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Vizag | Tirupati | Kolkata | Ahmedabad

For [B] = FFH  $\rightarrow$  256 times For [B] = FEH  $\rightarrow$  256 times For [B] = FDH  $\rightarrow$  256 times

For [B] =  $00H \rightarrow 256$  times  $\therefore$  loop executes for 256 × 256 times

#### 29. Ans: (b)

| Sol: | XRA A    | ; [A] = 00H, CY = 0             |

|------|----------|---------------------------------|

|      | ACI 05H  | ; $[A] = [A] + CY + 05H$        |

|      |          | = 05H = 00000101                |

|      | RLC      | ; [A] = 00001010 = 0AH, CY = 0  |

|      | MOV B, A | ; [B] = 0AH                     |

|      | RLC      | ; [A] = 00010100, CY = 0        |

|      | RLC      | ; [A] = 00101000, CY = 0        |

|      | ADD B    | ; $[A] \leftarrow [A] + [B]$    |

|      |          | 0010 1000                       |

|      |          | 0000 1010                       |

|      |          | +                               |

|      |          | $0\ 0\ 1\ 1$ $0\ 0\ 1\ 0 = 32H$ |

|      | MOV C, A | ; [C] = 32H                     |

#### **30.** Ans: (c)

**Sol:** The interrupt vector table consists of 256 number of 4-byte pointers, and resides in the first 1kB of addressable memory. Each interrupt number is reserved for a specific purpose.

#### 31. Ans: (a)

- **Sol:** There are total 9 flags in 8086

- (a) conditional or status flags : 6 flags

- 1. Sign flag (S)

- 2. Zero flag (Z)

- 3. Auxiliary carry flag (AC)

- 4. Parity flag (P)

- 5. Carry flag (CY)

- 6 Over flow flag (O)

- (b) Control flags : 3 flags

- 1. Directional flag (D)

- 2. Interrupt flag (I)

- 3. Trap flag (T)

#### **32.** Ans: (a)

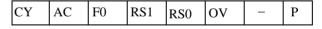

**Sol:** The flag register (program status word) of 8051 microcontroller is:

Carry flag (CY), auxiliary carry (AC), parity (P) and overflow (OV) are conditional flags.

$\therefore$  There is no zero flag in 8051.

- 33. Ans: (c)

- Sol: XRL operand 1, operand2: a bitwise "EXCLUSIVE OR" operation between operand1 and operand 2, leaving the resulting value in operand 1. Here, operand 1 is [A] = FFH

[A] ← FF ⊕ R6

So, it finds the 1's complement of R6 register.

ACE Engineering Academy

GATE+PSUs - 2020 Admissions Open From 14th NOV 2018

---- DELHI -

11th May | 23rd May 2019

### EARLY BIRD OFFER :

Register on or Before 31" December 2018 : 5000/- Off | Register on or Before 31" March 2019 : 3000/- Off

### **TEST YOUR PREP** IN A REAL TEST ENVIRONMENT

# Pre GATE - 2019

Date of Exam : 20<sup>th</sup> January 2019 Last Date to Apply : 31st December 2018

#### **Highlights** :

- \* Get real-time experience of GATE-2019 test pattern and environment.

- \* Virtual calculator will be enabled.

- \* Post exam learning analytics and All India Rank will be provided.

- \* Post GATE guidance sessions by experts.

- \* Encouraging awards for GATE-2019 toppers.

#### 34. Ans: (b)

**Sol:** The time delay for JNZ is 10T if it satisfies the condition otherwise it is 7T.

LOOP executes till the content of C register becomes 0, i.e., for 5 times.

For the first four times JNZ condition will not satisfies, so this instruction will take 10T states.

But during 5th time, JNZ satisfies, which takes 7T states.

$\begin{aligned} Delay &= T_O + T_L - 3T \\ &= 14T + (5 \times 26T) - 3T = 141 \ T \end{aligned}$

#### 35. Ans: (c)

- **Sol:** 1. READY is active high signal. When it is high, it indicates that the device is ready to transfer data. When it is low, it indicates wait state.

- 2. ALE is high only during T1. when ALE goes low, the address is saved and AD7 AD0 lines can be used for their purpose as the bi-directional data lines.

$\therefore$  Statements (1) & (2) are false

#### 36. Ans: (d)

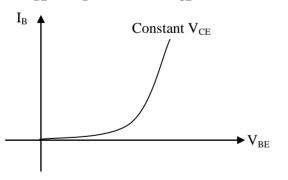

Sol: 1) In Common emitter configuration the input characteristics are plotted between  $V_{BE}$  and  $I_B$  at constant  $V_{CE}$ .

2) Common base configuration is acts as a current buffer whose input resistance is very low(zero ideally). So CB configuration has lower resistance compared to CE.

- 3) CB configuration has high voltage gain and its current gain is approximately 1.

- :Given three statements are incorrect.

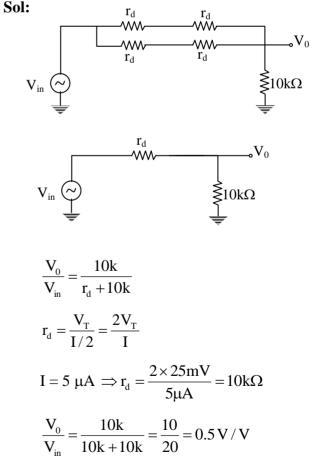

#### 37. Ans: (c) Sol:

| Type of power<br>amplifier | Conduction angle |

|----------------------------|------------------|

| Class-A                    | 360°             |

| Class-B                    | 180 °            |

| Class-AB                   | > 180 °          |

| Class-C                    | < 180            |

ACE Engineering Academy Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Kolkata | Vizag | Tirupati | Kukatpally

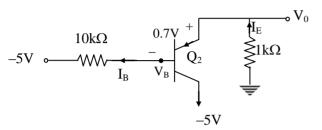

- **39.** Ans: (b)

- **Sol:** For  $V_i = -5V$  $(Q_2)$  gets ON,  $(Q_1)$  gets OFF

$Q_2$  is in active region  $V_{\rm B} = V_0 - 0.7$ Apply KVL  $I_E + 0.7 + 10I_B - 5 = 0$  $I_{\rm E} + 10 \left( \frac{I_{\rm E}}{100} \right) = 5 - 0.7$  $I_E = \frac{4.3}{1.1} = 3.9 \text{mA}$  $V_0 = -I_E(1k) = -3.9 V$

#### **40**. Ans: (b)

**Sol:**

$$f_{T} = \frac{g_{m}}{2\pi(C_{\pi} + C_{\mu})}$$

| 43.  | Ans: (d)                      |                                       |

|------|-------------------------------|---------------------------------------|

| Sol: | (A) Hartley oscillator        | : Inductive feedback is used          |

|      | (B) RC phase shift oscillator | : Pure sine wave output is possible   |

|      | (C) Wein bridge oscillator    | : Both positive and negative feedback |

|      | (D) Colpitt's oscillator      | : Capacitive feedback is used         |

#### Ans: (a) **44**.

Sol: Given that,

$$\frac{dA}{A} = \frac{10}{100} = 0.1$$

Variation in closed loop gain  $\frac{dA_f}{A_f} = \frac{0.1}{100} = 0.001$

Sensitivity factor  $= \frac{1}{1 + A\beta}$

Desensitivity factor  $= \frac{1}{\text{Sensitivit y}} = 1 + A\beta$

$$g_{m} = \frac{I_{CQ}}{V_{T}} = \frac{1mA}{25mV} = 0.04 \text{ A/V}$$

$$f_{T} = \frac{0.04}{2\pi \left(\frac{10\mu + 5\mu}{\pi}\right)} = \frac{4}{100 \times 2 \times 15\mu}$$

$$= \frac{4}{3 \times 10^{-3}} = 1.33 \text{ kHz}$$

41. Ans: (c)

Sol: Maximum voltage on secondary side

$$V_{\rm m} = 500\pi\sqrt{2} \times \frac{1}{2} = 250\pi\sqrt{2} \text{ Volts}$$

$$\left(V_{\rm dC}\right)_{\rm no \ load} = \frac{2V_{\rm m}}{\pi} = \frac{2 \times 250\pi\sqrt{2}}{\pi}$$

$$= 500\sqrt{2} \text{ Volts}$$

#### 42. Ans: (c)

Sol: Negative feedback in OP-amp reduces the voltage gain and makes the linear operations possible. Oscillations possible with positive

feedback.

Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Vizag | Tirupati | Kolkata | Ahmedabad ACE Engineering Academy

$$\frac{dA_{f}}{A_{f}} = \frac{1}{1 + A\beta} \frac{dA}{A}$$

$$0.001 = \frac{1}{1 + A\beta} (0.1)$$

$$1 + A\beta = \frac{0.1}{0.001} = 100$$

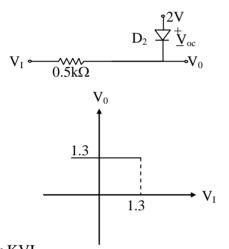

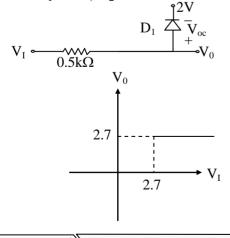

- 45. Ans: (b)

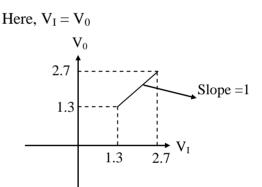

- Sol: Case: I

Consider D<sub>1</sub> - OFF, D<sub>2</sub> - ON

By KVL

$$2 - V_{oc} - V_I = 0 \Rightarrow V_{oc} = 2 - V_I$$

For D<sub>2</sub> ON  $\Rightarrow V_{oc} > 0.7$

$\Rightarrow 2 - V_I > 0.7$

$\Rightarrow V_I < 1.3$

$V_0 = 1.3$  Volts

Case: II

Consider D<sub>1</sub> - ON, D<sub>2</sub> - OFF

By KVL  $2 + V_{oc} - V_I = 0 \Rightarrow V_{oc} = V_I - 2$ For D<sub>1</sub> ON  $\Rightarrow V_{oc} > 0.7$   $\Rightarrow V_I - 2 > 0.7$   $\Rightarrow V_I > 2.7$  $V_0 = 2.7$  Volts

#### Case: III

Consider  $D_1$  - OFF &  $D_2$  – OFF Both diodes are OFF if  $1.3 < V_I < 2.7$

Hence by combining above three cases, the input-output characteristics is

46. Ans: (c)

Sol:  $I_{01} = I_{03} = I_{ref}$   $I_{04} = 3I_{ref}$   $I_{02} = 2I_{ref}$ Given that  $I_{02} = 200 \ \mu A$   $\Rightarrow I_{ref} = \frac{I_{02}}{2} = 100 \ \mu A$  $I_{04} = 3I_{ref} = 300 \ \mu A$

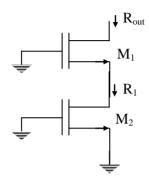

#### 47. Ans: (d) Sol:

Method-1

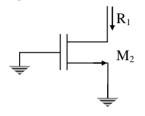

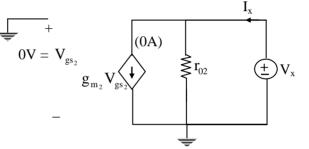

Finding R<sub>1</sub>:

$\frac{\mathbf{V}_{\mathbf{x}}}{\mathbf{I}_{\mathbf{x}}} = \mathbf{R}_1 = \mathbf{r}_{02}$

Replace  $M_2$  by  $r_{02}$

ACE Engineering Academy

Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Vizag | Tirupati | Kolkata | Ahmedabad

KCL at output node:

$$-I_{x} + g_{m1}V_{gs1} + \frac{V_{x} - I_{x}r_{02}}{r_{01}} = 0$$

$$-I_{x} + g_{m1}(0 - I_{x}r_{02}) + \frac{V_{x}}{r_{01}} - I_{x}\frac{r_{02}}{r_{01}} = 0$$

$$\frac{V_{x}}{r_{01}} = I_{x}\left[1 + g_{m1}r_{02} + \frac{r_{02}}{r_{01}}\right]$$

$$\frac{V_{x}}{I_{x}} = r_{01} + g_{m1}r_{01}r_{02} + r_{02} = R_{out}$$

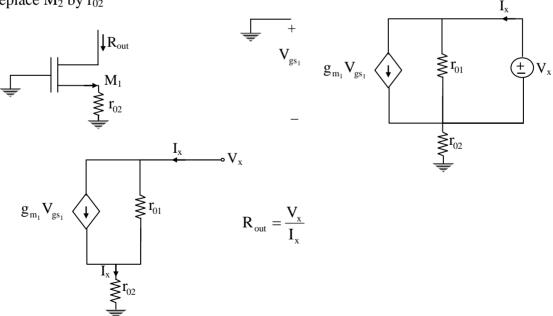

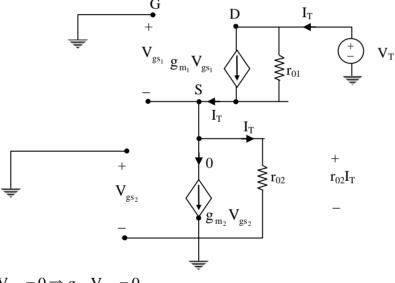

#### Method-2

Calculation of output Resistance  $(R_{out})$ ;  $(V_{in} = 0)$

:11:

Here,  $V_{gs_2} = 0 \Longrightarrow g_{m_2}V_{gs_2} = 0$  $\Rightarrow -V_{gs_1} - r_{02}I_T = 0 \Rightarrow V_{gs_1} = -r_{02}I_T$ By KVL  $V_{\rm T} - r_{01} (I_{\rm T} - g_{\rm m_1} V_{\rm gs_1}) - r_{02} I_{\rm T} = 0$  $\Longrightarrow \mathbf{V}_{\mathrm{T}} = \mathbf{r}_{01}\mathbf{I}_{\mathrm{T}} + \mathbf{g}_{\mathrm{m}_{1}}\mathbf{V}_{\mathrm{gs}_{1}}\mathbf{r}_{01} + \mathbf{r}_{02}\mathbf{I}_{\mathrm{T}}$  $\Rightarrow V_{T} = r_{01}I_{T} + g_{m_{1}}r_{01}r_{02}I_{T} + r_{02}I_{T}$  $\Longrightarrow \frac{V_{T}}{I_{T}} = r_{01} + r_{02} + g_{m}r_{01}r_{02}$  $\Rightarrow R_{out} = \frac{V_{T}}{I_{T}} = r_{01} + r_{02} + g_{m_{1}}r_{01}r_{02}$

ACE Engineering Academy Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Kolkata | Vizag | Tirupati | Kukatpally

### Launching Spark Batches for ESE / GATE - 2020 from Mid May 2019

Admissions from January 1st, 2019

## Launching Regular Batches for ESE / GATE - 2020

from Mid May 2019

Admissions from January 1st, 2019

48. Ans: (a)

Sol:

$$A_{f}(0) = \frac{A_{V}}{1 + \beta A_{V}}$$

$100 = \frac{10^{4}}{1 + \beta A_{V}}$

$1 + \beta A_{V} = \frac{10^{4}}{100} = 100$

$\omega_{Hf} = \omega_{H} (1 + \beta A_{V}) = 50 \times 100$

$= 5000 \text{ rad/sec}$

- 49. Ans: (c)

- Sol:  $V_{BCO}$  : Voltage across Base-collector junction when emitter open  $V_{BCO} = 70 \text{ V}$  $V_B - V_C |_{V_E=open} = 70 \text{ V}$  $10 - V_0 = 70$  $V_0 = -60 \text{ V}$

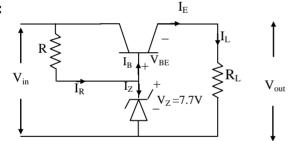

- 50. Ans: (d)

$$\begin{split} V_{out} &= V_Z - V_{BE} = 7.7 - 0.7 = 7V \\ V_{CE} &= V_{in} - V_{out} = 15 - 7 = 8V \\ I_R &= \frac{V_{in} - V_Z}{R} \\ &= \frac{15 - 7.7}{7.3k} = 1 \text{mA} = 1000 \mu\text{A} \\ I_L &= \frac{V_{out}}{R_L} = \frac{7}{3.5k} = 2 \text{mA} \\ I_B &= \frac{I_E}{1 + \beta} = \frac{2m}{100} = 20 \mu\text{A} \quad [\because I_E = I_L] \\ I_Z &= I_R - I_B = 1000 \mu - 20 \mu = 980 \ \mu\text{A} \end{split}$$

#### 51. Ans: (d)

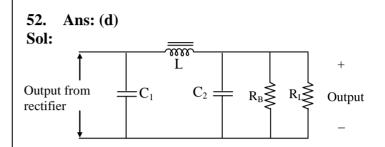

**Sol:** Ripple factor of power supply is a measure of purity of power output.

- When actual load is connected, there is a small additional voltage drop. Thus the difference between no load and full load voltage is reduced. Thus, voltage regulation is improved.

- (ii) Bleeder resistor improves the filtering action by maintaining a minimum current through the choke

- (iii)When a bleeder is not used and power supply is switched off, the capacitor retains its charge for some time which is dangerous for people working with equipment. This high voltage discharges through bleeder.

#### 53. Ans: (b)

#### Sol: In class B

- $\rightarrow$  For low signal voltage, Ic = 0

- $\rightarrow$  Cross- over distortion problem is there

#### In class AB

$\rightarrow$  Even for no signal, small current flows

Hence power drawn is not zero

#### 54. Ans: (b)

**Sol:** Monolithic ICs offer low power rating. So, statement(iii) is wrong statement.

ACE Engineering Academy Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Kolkata | Vizag | Tirupati | Kukatpally

#### 55. Ans: (a)

- **Sol:** (A) Thin and thick layer IC s are also known as printed film circuits because in their manufacturing silk-screen printing techniques are used.

- (B) Hybrid IC is combination of number of monolithic IC's. These are widely used for high power audio amplifier applications.

- (C) Linear IC's input and output relationship is linear. So used in amplifiers, oscillators etc

- (D) Digital IC's find wide applications in computers and logic circuits.

#### 56. Ans: (a)

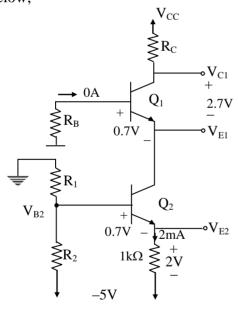

Sol:  $\beta = \infty$ , i.e. base currents are zero for both  $Q_1 \& Q_2$ . So, the circuit can be redrawn as below,

$$\begin{split} V_{E2} &= -5 + (2m \times 1k) = -3V \\ V_{BE2} &= 0.7V \\ V_{B2} - V_{E2} &= 0.7 \\ \Rightarrow V_{B2} &= 0.7 + V_{E2} = 0.7 - 3 \\ V_{B2} &= -2.3V \\ V_{BE1} &= 0.7 V \\ V_{B1} - V_{E1} &= 0.7 \\ 0 - V_{E1} &= 0.7 \end{split}$$

$$\begin{split} V_{E1} &= -\ 0.7\ V\\ \text{Given that}\ V_{C1} &= 2.7\ V\\ V_{C1} &- V_{E1} &= 2.7\ V\\ V_{C1} &= 2.7\ + V_{E1}\\ &= 2.7\ - 0.7\\ &= 2\ V\\ \hline \frac{V_{E2}}{V_{C1}} &= \frac{-3}{2} = -1.5 \end{split}$$

57. Ans: (b)

Sol:

$$-V_{CC} + I_B R_B + V_{BE} + I_E R_E = 0$$

$V_{CC} - I_B R_B - V_{BE} - (I_B + I_C) R_E = 0$

$V_{CC} - I_B (R_B + R_E) - V_{BE} - I_C R_E = 0$

$I_B = \frac{V_{CC} - V_{BE} - I_C R_E}{R_B + R_E}$

$\frac{dI_B}{dI_C} = \frac{-R_E}{R_B + R_E}$

$S = \frac{1 + \beta}{1 - \beta \frac{dI_B}{dI_C}}$

$S = \frac{1 + \beta}{1 - \beta \frac{R_E}{R_E + R_B}}$

$= \frac{1 + 99}{1 + 99(\frac{1}{10})}$

$$=\frac{100}{10.9}$$

= 9.17

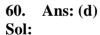

#### 58. Ans: (d)

**Sol:** The node at which input is given is same as the feedback taken node. So shunt at input. If the feedback node is at one node and output taken from another node, then it is said to be Series at output.

ACE Engineering Academy Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Vizag | Tirupati | Kolkata | Ahmedabad

59. Ans: (c) **Sol:**  $i_D = \frac{1}{2} K'_n \frac{W}{L} (V_{GS} - V_T)^2$ At  $i_D = 1mA$  $\Rightarrow 1m = \frac{1}{2} K'_n \frac{W}{L} (-1 - V_T)^2 \dots (1)$ At  $i_D = 9mA$  $\Rightarrow 9m = \frac{1}{2}K'_{n}\frac{W}{I}(I-V_{T})^{2}\dots(2)$  $\frac{(2)}{(1)} \Rightarrow \frac{9}{1} = \frac{(1 - V_T)^2}{(1 + V_T)^2}$  $\frac{1 - V_{T}}{1 + V_{T}} = \pm 3$  $\frac{1 - V_{T}}{1 + V_{T}} = 3$  $\frac{1 - V_{\rm T}}{1 + V_{\rm T}} = -3$  $1 - V_T = 3 + 3V_T$  $1 - V_T = -3 - 3V_T$  $4V_{T} = -2$  $-2V_{T} = 4$  $V_T = -2V$  $V_{\rm T} = -0.5 V$  $V_{GS} = -1V < V_T$ So  $V_T = -0.5$  not possible  $\therefore$  V<sub>T</sub> = -2V

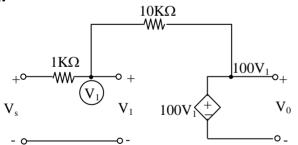

KCL

$$\frac{V_{s} - V_{1}}{1K} = \frac{V_{1} - 100V_{1}}{10K}$$

$$10V_{s} - 10V_{1} = -99V_{1}$$

$$10V_{s} = -89V_{1}$$

$$\rightarrow V_{1} = \frac{-10}{89}V_{s}$$

$$V_{0} = 100V_{1} = 100\left[\frac{-10}{89}\right]V_{S}$$

$$\frac{V_{0}}{V_{S}} = \frac{-1000}{89}$$

61. Ans: (d)

Sol:  $\beta = \frac{SL_{1}}{SL_{2}} = \frac{L_{1}}{L_{2}}$

$$A = \frac{-R_{F}}{R_{1}}; A = \frac{1}{\beta} \text{ for sustained oscillations})$$

$$\left|\frac{-R_{F}}{R_{1}}\right| = \frac{L_{2}}{L_{1}}$$

$$\frac{R_{F}}{2k} = \frac{5mH}{2mH}$$

#### 62. Ans: (b)

$R_F = 5k\Omega$

**Sol:** 1. In 555 timers, threshold level is  $\frac{2}{2}V_{CC}$

- 2. -ve trigger pulse is required to change the output state in monostable multivibrator

- 3. One of the application of 555 in Astable modes FSK generation

- 4. In Schmitt trigger using 555 timer,  $V_{UTP} = \frac{V_{CC}}{\epsilon}$  and  $V_{LTP} = -\frac{V_{CC}}{\epsilon}$

#### 63. Ans: (b)

#### **Sol: Step (1):**

Effective voltage applied at the inverting input terminal of op-amp

$$= \frac{10k \times 12V}{10k + 10k} = 6V \dots (1)$$

#### **Step (2):**

For the output of op-amp to be positive, the input at non-inverting terminal of op-amp should of more than 6 V, i.e  $V_i > 6$  V---- (2) **Step (3):**

In the op-amp circuit shown, for the LED to turn ON, the output of op-amp should be positive. To get this +ve output,  $V_i > 6 V$

demy 💦 Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Kolkata | Vizag | Tirupati | Kukatpally

#### 64. Ans: (c)

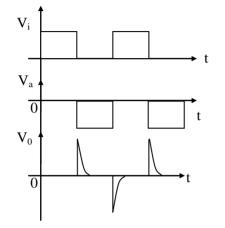

Sol: In the circuit a half wave rectifier and a differentiator is cascaded when we give a square-wave input to the half-wave rectifier, the output voltage  $V_0$  is shown below.

The differentiator, the voltage  $V_a$  is to be differentiate and results a output voltage,  $V_0$  which is impulse (spikes) wave as shown above.

#### 65. Ans: (c)

**Sol:** Voltage at non-inverting terminal

$$V_{p} = \frac{V_{1} + V_{2} + V_{3} + V_{4}}{4}$$

$$V_{p} \left[\frac{1}{R} + \frac{1}{R_{f}}\right] = \frac{V_{0}}{R_{f}}$$

$$\frac{1}{4} \left[\frac{1}{R} + \frac{1}{R_{f}}\right] = \frac{1}{R_{f}}$$

$$\Rightarrow \frac{1}{R} + \frac{1}{R_{f}} = \frac{4}{R_{f}}$$

$$\Rightarrow R = \frac{R_{f}}{3}$$

#### 66. Ans: (b)

Sol:  $\rightarrow$  JFET has low resistance (R<sub>GS</sub>) compared to MOSFET.

So, the statement (a) is wrong.

$$\rightarrow$$

g<sub>m</sub> of JFET is maximum when V<sub>GS</sub>= 0

$$\mathbf{I}_{\mathrm{D}} = \mathbf{I}_{\mathrm{DSS}} \left( 1 - \frac{\mathbf{V}_{\mathrm{GS}}}{\mathbf{V}_{\mathrm{P}}} \right)^2$$

$$\begin{split} g_{\rm m} &= \frac{\partial I_{\rm D}}{\partial V_{\rm GS}} = \frac{2 I_{\rm DSS}}{\left|V_{\rm P}\right|} \left(1 - \frac{V_{\rm GS}}{V_{\rm P}}\right) \\ g_{\rm m} &= g_{\rm m0} \! \left(1 - \frac{V_{\rm GS}}{V_{\rm P}}\right) \end{split}$$

The above  $g_m$  is maximum when  $V_{GS} = 0$

- → Elbers-Moll model can be used for both npn and pnp transistors

- → Usually FET has infinite resistance between gate and source

#### 67. Ans: (b)

**Sol:** The Gate can be self aligned to source and drain in a MOSFET with polysilicon gate. So it is preferred than a MOSFET with Aluminium gate. Overload and peak current handling capability is high

#### 68. Ans: (d)

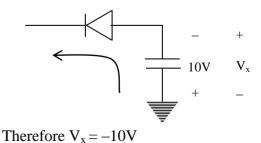

Sol: Positive cycle the first capacitor charges to peak of 5v, During negative cycle  $D_1$  is RB,  $D_2$  is FB capacitor charges to 10V in the polarity shown

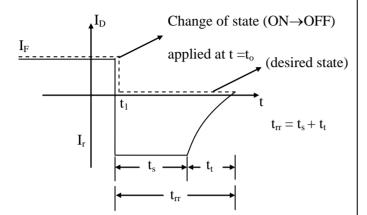

#### 69. Ans: (c) Sol: Reverse recovery time (t<sub>rr</sub>):

Where t<sub>rr</sub>: reverse recovery time

- t<sub>s</sub>: Storage time

- t<sub>t</sub>: transition time

Diffusion capacitance exist in forward biasregion and transition capacitance exist in reverse-bias region.

#### 70. Ans: (c)

- **Sol:** (1) The cross over distortion is eliminated in a push-pull amplifier by providing a small forward bias to the transistor.

- (2) The harmonic distortion refers to the non-sinusoidal nature of a periodic wave form and it defined at periodic frequency and multiple of that frequency.

$\therefore$  The statement(1) and (2) are correct statements.

- 71. Ans: (b)

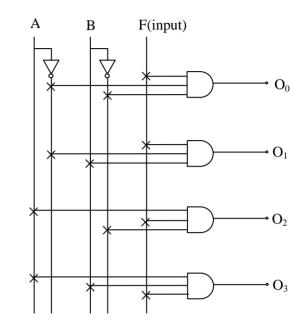

- Sol: Demultiplexer using AND gates

Where A, B are control inputs  $O_0, O_1, O_2, O_3$  are outputs

A demultiplexer can be used as decoder and demultiplexer can be built by AND gates. Statement (I) is true. Statement (II) is also true, but not giving correct explanation for I

#### 72. Ans: (b)

**Sol:** In I<sup>2</sup>L logic all individual transistors of RTL are replaced by multi collector transistors.

$\therefore$  Both statements are true but statement(II) is not giving correct explanation for statement(I).

#### 73. Ans: (d)

**Sol:** DMA is a process where the data is transferred between two peripherals directly without the involvement of the microprocessor.

$\therefore$  statement (I) is false & statement (II) is true

ACE Engineering Academy

#### 74. Ans: (d)

Sol: Blocking oscillator is a relaxation oscillator which generates short time duration pulse using a transistor as an active device.

∴ Statement (I) is false.

Blocking oscillators are used to generate pulses of large peak power.

∴ Statement (II) is true.

75. Ans: (d)

Sol: Zener regulator has low efficiency for heavy load currents as there is a considerable power loss in R.

V<sub>out</sub> = V<sub>Z</sub> + I<sub>Z</sub> Z<sub>I</sub>

The regulator is used only when there are small variations in load current and input voltage.

$\therefore$  Statement (I) is wrong and statement (II) is true.

ACE Engineering Academy Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Lucknow | Patna | Bengaluru | Chennai | Vijayawada | Vizag | Tirupati | Kolkata | Ahmedabad