# ELECTRONICS & COMMUNICATION ENGINEERING

# **DIGITAL CIRCUITS & MICROPROCESSORS**

**Volume-1 : Study Material with Classroom Practice Questions**

Number Systems

Chapter

(Solutions for Vol-1\_Classroom Practice Questions)

| 01.  | Ans: (d)                                                                                                                                                                                                                                                                                                 | 03. Ans: (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sol: | $135_{x} + 144_{x} = 323_{x}$ $(1 \times x^{2} + 3 \times x^{1} + 5 \times x^{0}) + (1 \times x^{2} + 4 \times x^{1} + 4 \times x^{0})$ $= 3x^{2} + 2x^{1} + 3x^{0}$ $\Rightarrow x^{2} + 3x + 5 + x^{2} + 4x + 4 = 3x^{2} + 2x + 3$ $x^{2} - 5x - 6 = 0$                                                | <b>Sol:</b> In 2's complement representation the sign bit can be extended towards left any number of times without changing the value. In given number the sign bit is 'X <sub>3</sub> ', hence it can be extended left any number of times.                                                                                                                                                                                                                                                             |

|      | x = 3x = 6 = 0<br>(x-6) (x+1) = 0 (Base cannot be negative)<br>Hence x = 6.<br>(OR)<br>As per the given number x must be greater<br>than 5. Let consider x = 6<br>$(135)_6 = (59)_{10}$<br>$(144)_6 = (64)_{10}$<br>$(323)_6 = (123)_{10}$<br>$(59)_{10} + (64)_{10} = (123)_{10}$<br>So that x = 6      | 04. Ans: (c)<br>Sol: Binary representation of $+(539)_{10}$ :<br>$2 \frac{539}{2 269 - 1}$<br>$2 \frac{134 - 1}{2 67 - 0}$<br>$2 \frac{33 - 1}{2 16 - 1}$<br>$2 \frac{16 - 1}{2 2 - 0}$<br>$1 \frac{-0}{2 2 - 0}$<br>$(+539)_{10} = (10000 \ 11 \ 0 \ 11)_2 = (00100 \ 0011011)_2$                                                                                                                                                                                                                       |

| 02.  | Ans: (a)                                                                                                                                                                                                                                                                                                 | $2^{\circ}S \text{ complement } \rightarrow 110111100101$                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Sol: | 8-bit representation of<br>$+127_{10} = 01111111_{(2)}$<br>1's complement representation of<br>-127 = 10000000.<br>2's complement representation of<br>-127 = 10000001.<br>No. of 1's in 2's complement of<br>-127 = m = 2<br>No. of 1's in 1's complement of<br>-127 = n = 1<br>$\therefore$ m: n = 2:1 | Hexadecimal equivalent $\rightarrow$ (DE5) <sub>H</sub><br>1995<br>05. Ans: 5<br>Sol: Symbols used in this equation are 0,1,2,3<br>Hence base or radix can be 4 or higher<br>$(312)_x = (20)_x (13.1)_x$<br>$3x^2 + 1x + 2x^0 = (2x+0) (x+3x^0+x^{-1})$<br>$3x^2+x+2 = (2x) \left(x+3+\frac{1}{x}\right)$<br>$3x^2+x+2 = 2x^2+6x+2$<br>$x^2-5x = 0$<br>x(x-5) = 0<br>x = 0(or) x = 5<br>x  must be  x > 3, So $x = 5rgaluru  Lucknow  Patna Chennai  Vijayawada  Vizag   Tirupati  Kukatpally   Kolkata$ |

| ACE<br>Engineering Publications                                                                                                                                                                                                             | :3:                                                                                                     | Number Systems                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Ans: 3<br>$123_5 = x8_y$<br>$1 \times 5^2 + 2 \times 5^1 + 3 \times 5^0 = x.y^1 + 8 \times y^0$<br>25 + 10 + 3 = xy + 8<br>$\therefore xy = 30$<br>Possible solutions:<br>i. $x = 1, y = 30$<br>ii. $x = 2, y = 15$<br>iii. $x = 3, y = 10$ | 07. Ans: 1<br>Sol: The range (<br>For 2's com<br>For sign ma<br>Let $n = 2 = -(2^{2-1})$ to<br>-2 to +1 | for) distinct values<br>nplement $\Rightarrow -(2^{n-1})$ to $+(2^{n-1}-1)$ |

| <br>3 possible solutions exists.                                                                                                                                                                                                            | $R   N \subseteq X - Y = 1$                                                                             |                                                                             |

# Logic Gates & Boolean Algebra

# 01. Ans: (c)

Chapter

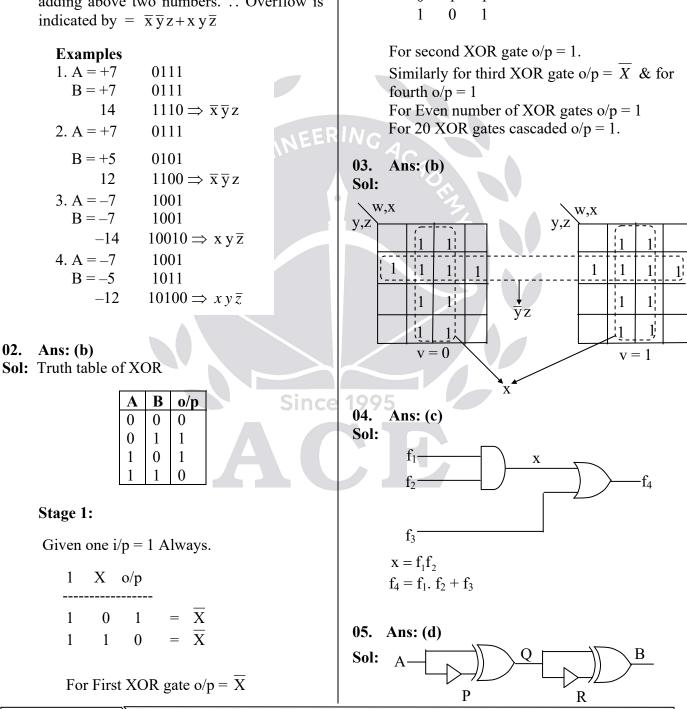

Sol: Given 2's complement numbers of sign bits are x & y. z is the sign bit obtained by adding above two numbers.  $\therefore$  Overflow is indicated by =  $\overline{x} \overline{y} z + x y \overline{z}$  Stage 2: <u>X</u> X o/p <u>0 1 1</u>

# 07. Ans: 3

# Chapter 4 Combinational Circuits

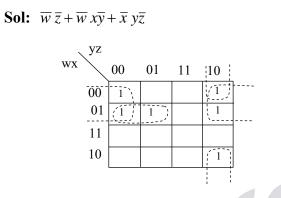

01. Ans: (d) **Sol:** Let the output of first MUX is " $F_1$ "  $F_1 = AI_0 + AI_1$ Where A is selection line,  $I_0$ ,  $I_1 = MUX$  Inputs  $F_1 = \overline{S}_1 \cdot W + S_1 \cdot \overline{W} = S_1 \oplus W$ Output of second MUX is  $F = \overline{A}.I_0 + A.I_1$  $\mathbf{F} = \overline{\mathbf{S}}_2.\mathbf{F}_1 + \mathbf{S}_2.\overline{\mathbf{F}}_1$  $\mathbf{F} = \mathbf{S}_2 \oplus \mathbf{F}_1$ But  $F_1 = S_1 \oplus W$  $\mathbf{F} = \mathbf{S}_2 \oplus \mathbf{S}_1 \oplus \mathbf{W}$ i.e.,  $F = W \oplus S_1 \oplus S_2$ 02. Ans: 50 Since 1995 Sol: Y<sub>3</sub> X<sub>3</sub>  $Y_2 X_2$  $Y_0 X_0$  $Z_4$  . FA<sub>3</sub>  $FA_2$  $FA_1$ FA<sub>0</sub>  $Z_0$  $S_3$  $S_2^{\dagger}$  $S_0$  $S_1$

Initially all the output values are '0', at t = 0, the inputs to the 4-bit adder are changed to  $X_3X_2X_1X_0 = 1100$ ,  $Y_3Y_2Y_1Y_0 = 0100$

---- indicates critical path delay to get the output

Digital

## 03. Ans: (a)

**Sol:** The given circuit is binary parallel adder/subtractor circuit. It performs A+B, A–B but not A + 1 operations.

| K | C <sub>0</sub> | Operation                                           |

|---|----------------|-----------------------------------------------------|

| 0 | 0              | A+B (addition)                                      |

| 0 | 1              | A+B+1(addition with carry)                          |

| 1 | 0              | $A + \overline{B}$ (1's complement addition)        |

| 1 | 1              | $A + \overline{B} + 1$ (2's complement subtraction) |

# 04. Ans: (d)

Sol: It is expansion of 2:4 decoders to 1:8 demultiplexer  $A_1$ ,  $A_0$  must be connected to  $S_1$ ,  $S_0$  i.e.,  $R = S_0$ ,  $S = S_1$

Since 1995

Q must be connected to  $S_2$  i.e.,  $Q = S_2$

P is serial input must be connected to D<sub>in</sub>

# 05. Ans: 6

Sol:  $T = 0 \rightarrow NOR \rightarrow MUX \ 1 \rightarrow MUX \ 2 \\ 2ns \ 1.5ns \ 1.5ns$ Delay = 2ns + 1.5ns + 1.5ns = 5ns  $T = 1 \rightarrow NOT \rightarrow MUX \ 1 \rightarrow NOR \rightarrow MUX \ 2 \\ 1ns \ 1.5ns \ 2ns \ 1.5ns$ Delay = 1ns + 1.5ns + 2ns + 1.5ns = 6nsHence, the maximum delay of the circuit is 6ns

# 06. Ans: -1

Sol: When all bits in 'B' register is '1', then only it gives highest delay.

$\therefore$  '-1' in 8 bit notation of 2's complement is 1111 1111

# Sequential Circuits

## 01. Ans: (c)

Chapter

## 02. Ans: 4

**Sol:** In the given first loop of states, zero has repeated 3 times. So, minimum 4 number of Flip-flops are needed.

## 03. Ans: 7

Sol: The counter is cleared when  $Q_D Q_C Q_B Q_A = 0110$

| Clk              | QD | Qc | QB | QA |

|------------------|----|----|----|----|

| 0                | 0  | 0  | 0  | 0  |

| 1                | 0  | 0  | 0  | 1  |

| 2                | 0  | 0  | 1  | 0  |

| 2<br>3           | 0  | 0  | 1  | 1  |

| 4                | 0  | 1  | 0  | 0  |

| 5                | 0  | 1  | 0  | 1  |

| 4<br>5<br>6<br>7 | 0  | 1  | 1  | 0  |

| 7                | 0  | 0  | 0  | 0  |

As the clear input is given to be synchronous so it waits upto the next clock pulse to clear the counter & hence the counter get's cleared during the 7<sup>th</sup> clock pulse.

$\therefore$  mod of counter = 7

# 04. Ans: (b)

$2\Delta t$ .

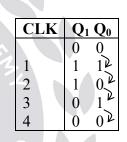

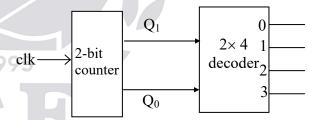

Sol: The given circuit is a mod 4 ripple down counter.  $Q_1$  is coming to 1 after the delay of

Outputs of counter is connected to inputs of decoder

| Coun           | ter outputs | Decoder inputs |   | De             | code  | r outp | outs  |

|----------------|-------------|----------------|---|----------------|-------|--------|-------|

| $\mathbf{Q}_1$ | $Q_0$       | а              | b | d <sub>3</sub> | $d_2$ | $d_1$  | $d_0$ |

| 0              | 0           | 0              | 0 | 0              | 0     | 0      | 1     |

| 0              | 1           | 0              | 1 | 0              | 0     | 1      | 0     |

| 1              | 0           | 1              | 0 | 0              | 1     | 0      | 0     |

| 1              | 1           | 1              | 1 | 1              | 0     | 0      | 0     |

The overall circuit acts as 4-bit ring counter n = 2

$\therefore$  k = 2<sup>2</sup> = 4, k-bit ring counter

| Barr 1911   | 6                        |                                                                                                |                                                                                     |                                 |                             |                                                                       |                  |                                                     |                                                      |

|-------------|--------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------|-----------------------------|-----------------------------------------------------------------------|------------------|-----------------------------------------------------|------------------------------------------------------|

| 06.<br>Sol: | Ans: (b)                 |                                                                                                |                                                                                     | 07.<br>Sol:                     | Ans                         | : (b)                                                                 |                  |                                                     |                                                      |

|             | CLK                      | Serial in=<br>$B \oplus C \oplus D$                                                            | ABCD                                                                                | ~ • • •                         | J                           | K Q                                                                   | $\overline{Q}_n$ | $T = (J + Q_n)$                                     | $Q_{n+1}$                                            |

|             | 0                        | 1                                                                                              | 1 0 1 0<br>1 1 0 1                                                                  |                                 |                             |                                                                       |                  | $\left(\mathbf{K}+\overline{\mathbf{Q}}_{n}\right)$ |                                                      |

|             | 1 2                      | $0 \longrightarrow 1$                                                                          | $     \begin{array}{c}       1 & 1 & 0 & 1 \\       0 & 1 & 1 & 0     \end{array} $ |                                 | 0                           | 0 0                                                                   | 1                | 0.1 = 0                                             | 0 ]                                                  |

|             | 3                        | 0                                                                                              | 0 0 1 1                                                                             |                                 | 0                           | $     \begin{array}{c c}       0 & 1 \\       1 & 0     \end{array} $ | 0                | 1.0 = 0<br>0.1 = 0                                  | $1 \int Q_n$                                         |

|             | 4                        | $0 \longrightarrow$                                                                            | 0 0 0 1                                                                             |                                 | 0                           | $\frac{1}{1}$ 1                                                       | 0                | 0.1 = 0<br>1.1 = 1                                  | $\begin{bmatrix} 0\\0 \end{bmatrix}_0$               |

|             | 5<br>6                   | $1 \longrightarrow 0 \longrightarrow 1$                                                        | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                |                                 | 1                           | 0 0                                                                   | 1                | 1.1 = 1                                             | 1 ጊ                                                  |

|             | 7                        | $1 \longrightarrow$                                                                            | 1010                                                                                | 200                             | 1                           | 0 1                                                                   | 0                | 1.0 = 0                                             | $1^{\int}1$                                          |

|             |                          |                                                                                                |                                                                                     |                                 | 1                           | $     \begin{array}{c c}       1 & 0 \\       1 & 1     \end{array} $ | 1                | 1.1 = 1<br>1.1 = 1                                  | $\begin{bmatrix} 1\\ 0 \end{bmatrix} \overline{Q}_n$ |

|             | .:. After                | 7 clock pulses                                                                                 | content of shift                                                                    | t                               | Ľ                           |                                                                       |                  | 1.1 - 1                                             | $0^{2} Q_{n}$                                        |

|             |                          | ecome 1010 agai                                                                                |                                                                                     | RING                            | JKC                         | $Q_n 00$                                                              | 01               | 11 1                                                | 0                                                    |

|             |                          |                                                                                                | ENO                                                                                 |                                 | 0                           | 70                                                                    |                  | $\langle \hat{1} \rangle$                           |                                                      |

|             |                          |                                                                                                | <u>ි</u> රු                                                                         |                                 |                             | - 2                                                                   |                  |                                                     |                                                      |

|             |                          |                                                                                                | र                                                                                   |                                 | 1                           | 1)                                                                    |                  | <u>``</u> []/                                       | (1                                                   |

|             |                          |                                                                                                |                                                                                     |                                 | <u> </u>                    |                                                                       |                  | _                                                   | I                                                    |

|             |                          |                                                                                                |                                                                                     |                                 | T = .                       | $J Q_n + J$                                                           | $KQ_n =$         | $(J+Q_n)(K+\overline{Q_n})$                         | )                                                    |

| 08.         | Ans: 1.5                 |                                                                                                |                                                                                     |                                 |                             | $\searrow$                                                            |                  |                                                     |                                                      |

| Sol:        | 1115. 1.0                | $Clk$ $Q_1$ $Q_2$                                                                              | 2 Q3 Q4 Q5                                                                          | $Y = Q_3$                       | +0                          | 1                                                                     |                  |                                                     |                                                      |

|             |                          | $\begin{array}{c c} Clk & Q_1 & Q_2 \\ \hline 0 & 0 & 1 \\ \end{array}$                        | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                               | $1-Q_3$                         | 1 Q5                        | - /                                                                   |                  |                                                     |                                                      |

|             |                          | $\begin{vmatrix} 0 \\ 1 \end{vmatrix} = 0$                                                     |                                                                                     |                                 |                             |                                                                       |                  |                                                     |                                                      |

|             |                          |                                                                                                |                                                                                     | :e0199                          | 5                           |                                                                       |                  |                                                     |                                                      |

|             |                          | $\begin{vmatrix} 2 \\ 3 \end{vmatrix} = 0$                                                     | 0 $1$ $0$ $1$ $0$ $1$ $1$ $1$ $1$ $1$ $1$ $1$ $1$ $1$ $1$                           | 1                               |                             |                                                                       |                  |                                                     |                                                      |

|             |                          |                                                                                                |                                                                                     | 1                               |                             |                                                                       |                  |                                                     |                                                      |

|             |                          | 5 0 1                                                                                          |                                                                                     | 0                               |                             |                                                                       |                  |                                                     |                                                      |

|             | The wave                 | form at OR gate                                                                                | output, Y is [A =                                                                   | +5V1                            |                             |                                                                       |                  |                                                     |                                                      |

|             |                          |                                                                                                |                                                                                     |                                 |                             |                                                                       |                  |                                                     |                                                      |

|             |                          | 0 T 2T 3T                                                                                      | 4T 5T                                                                               | <b>,</b>                        | •                           |                                                                       |                  |                                                     |                                                      |

|             |                          | $\blacksquare$ T <sub>1</sub> = 5T                                                             | ►                                                                                   |                                 |                             |                                                                       |                  |                                                     |                                                      |

|             | Average p                |                                                                                                | _                                                                                   |                                 |                             |                                                                       |                  |                                                     |                                                      |

|             | $P = \frac{V_{Ao}^2}{R}$ | $\dot{F} = \frac{1}{R} \left[ \frac{Lt}{T_1 \to \infty} \frac{1}{T_1} \int_0^{T_1} dt \right]$ | $y^{2}(t) dt = \frac{1}{RT_{1}} \left[ \int$                                        | $\int_{T}^{2T} A^2 dt +$        | $\int_{3T}^{5T} \mathbf{A}$ | $^{2}$ dt                                                             |                  |                                                     |                                                      |

|             | $=\frac{A^2}{RT_1}$      | -[(2T-T)+(5T)]                                                                                 | $-3T)] = \frac{A^2.3T}{R(5T)} =$                                                    | $\frac{5^2.3}{10 \times 5} = 1$ | .5 mw                       | V                                                                     |                  |                                                     |                                                      |

| ACE         | Engg. Publicatio         | ons Hyderabad   Delhi                                                                          | Bhopal  Pune  Bhubaneswar                                                           | Bengaluru  Luc                  | know   P                    | atna   Chenna                                                         | i  Vijayawa      | uda  Vizag   Tirupati  Kuka                         | tpally   Kolkata                                     |

|             |                          |                                                                                                |                                                                                     |                                 |                             |                                                                       |                  |                                                     |                                                      |

## 09. Ans: (b)

Sol:

| Present | Next State |       | Output (Y)       |       |  |

|---------|------------|-------|------------------|-------|--|

| State   | X = 0      | X = 1 | $\mathbf{X} = 0$ | X = 1 |  |

| А       | Α          | Е     | 0                | 0     |  |

| В       | С          | Α     | 1                | 0     |  |

| С       | В          | Α     | 1                | 0     |  |

| D       | Α          | В     | 0                | 1     |  |

| Е       | Α          | С     | 0                | 1     |  |

# Step (1):

By replacing state B as state C then state

B, C are equal.

| Reducing stat | e table | <u>ک</u> |

|---------------|---------|----------|

| Present state | Next s  | tate     |

|               | X = 0   | X = 1    |

| A             | Α       | Е        |

| В             | В       | А        |

| В             | В       | А        |

| D             | A       | В        |

| E             | Α       | В        |

|               |         |          |

Step (2):

| Reducing state table |            |       |  |  |

|----------------------|------------|-------|--|--|

| Present state        | Next state |       |  |  |

|                      | X = 0      | X = 1 |  |  |

| А                    | А          | Е     |  |  |

| В                    | В          | А     |  |  |

| D                    | А          | В     |  |  |

| E                    | А          | В     |  |  |

|                      |            |       |  |  |

State D, E are equal, remove state E and replace E with D in next state.

| Reducing state table |                          |   |  |

|----------------------|--------------------------|---|--|

| Present state        | Present state Next state |   |  |

|                      | X = 0  X = 1             |   |  |

| А                    | А                        | D |  |

| В                    | В                        | А |  |

| D                    | А                        | В |  |

| D                    | А                        | В |  |

Finally reduced state table is

|    | Reduced state table      |       |       |  |  |

|----|--------------------------|-------|-------|--|--|

|    | Present state Next state |       |       |  |  |

| C. | 9                        | X = 0 | X = 1 |  |  |

|    | A                        | А     | D     |  |  |

|    | В                        | В     | А     |  |  |

|    | D                        | Α     | В     |  |  |

|    |                          |       |       |  |  |

$\therefore$  3 states are present in the reduced state table

# 10. Ans: (c)

Sol: State table for the given state diagram

|   | State                 | Input | Output |

|---|-----------------------|-------|--------|

| 5 | S <sub>0</sub>        | 0     | 1      |

|   | S <sub>0</sub>        | 1     | 0      |

|   | <b>S</b> <sub>1</sub> | 0     | 1      |

|   | $S_1$                 | 1     | 0      |

Output is 1's complement of input.

# 11. Ans: (c)

Sol: In state (C), when XYZ = 111, then Ambiguity occurs Because, from state (C)  $\Rightarrow$  When X = 1, Z = 1 $\Rightarrow$  N.S is (A) When  $Y = 1, Z = 1 \Rightarrow$  N.S is (B)

ACE Engg. Publications Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Bengaluru | Lucknow | Patna | Chennai | Vijayawada | Vizag | Tirupati | Kukatpally | Kolkata

Since 199

# Logic Gate Families

# Chapter

### 01. Ans: (D)

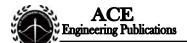

# Sol: V<sub>OH</sub>(min):-

(High level output voltage)

The minimum voltage level at a Logic circuit output in the logic '1' state under defined load conditions.

# Vol(max):-

(Low level output voltage)

The maximum voltage level at a logic circuit output in the Logical '0' state under defined load conditions.

# V<sub>IL</sub>(max):- (Low level input voltage)

The maximum voltage level required for a logic '0' at an input. Any voltage above this level will not be accepted as a Low by the logic circuit.

# V<sub>IH</sub>(min) :- (High level Input voltage)

The minimum voltage level required for logic '1' at an input. Any voltage below this level will not be accepted as a HIGH by the Logic circuit.

<u>V</u>ol Ŷı∟ Low Fig: currents and voltages in the two logic

states.

199 nce

$$OUT = \overline{(\overline{PQ})} = PQ$$

$$= P \text{ AND } Q$$

### 05. Ans: (b)

**Sol:** As per the description of the question, when the transistor Q<sub>1</sub> and diode both are OFF then only output z = 1.

| Χ | Y | Ζ | Remarks                             |

|---|---|---|-------------------------------------|

| 0 | 0 | 0 | $Q_1$ is OFF, Diode is ON           |

| 0 | 1 | 1 | Q <sub>1</sub> is OFF, Diode is OFF |

| 1 | 0 | 0 | $Q_1$ is ON, Diode is OFF           |

| 1 | 1 | 0 | Q <sub>1</sub> is ON, Diode is OFF  |

# Hence $Z = \overline{X}Y$

ACE Engg. Publications Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Bengaluru | Lucknow | Patna | Chennai | Vijayawada | Vizag | Tirupati | Kukatpally | Kolkata

# 02. Ans: (b)

**Sol:** Fan out is minimum in DTL

(High Fan-out = CMOS)

Power consumption is minimum in CMOS. Propagation delay is minimum in ECL (fastest = ECL)

# 03. Ans: (b)

Sol: When  $V_i = 2.5V$ ,

$Q_1$  is in reverse active region

- Q<sub>2</sub> is in saturation region

- Q<sub>3</sub> is in saturation region

- Q<sub>4</sub> is in cut-off region

# 04. Ans: (d)

Sol: The given circuit can be redrawn as below:

$\circ V_{dd}$

•OUT

NOT gate

# **Semiconductor Memories**

# Chapter

- 01. Ans: (b) Sol: Square of a 4 - bit number can be at most 8 - bit number.  $\{ i.e (1111)_2 = (15)_{10} \}$

- $[(15)_{10}]^2 = (225)_{10}\}.$

Therefore ROM requires 8 data lines.

Data is with size of 4 bits

ROM must require 4 address lines and 8 data lines

$ROM = 2^n \times m$

n = inputs (address lines), m = output lines n = 4, m = 8.

# 02. Ans: (a)

**Sol:** ROM is used to design a combinational circuit. The number of address lines of the ROM is equal to the number of input variables in the truth table.

ROM is represented as  $2^n \times m$  where  $2^n$  inputs and m output lines.

[Where n = address bits]

03. Ans: (b)

| 8              | 4     | 2     | 1     | 2              | 4       | 2     | 1              | 2421        |

|----------------|-------|-------|-------|----------------|---------|-------|----------------|-------------|

| i/p s          |       |       |       | 0/1            | Outputs |       |                |             |

| X <sub>3</sub> | $X_2$ | $X_1$ | $X_0$ | Y <sub>3</sub> | $Y_2$   | $Y_1$ | Y <sub>0</sub> |             |

| 0              | 0     | 0     | 0     | 0              | 0       | 0     | 0              | 0           |

| 0              | 0     | 0     | 1     | 0              | 0       | 0     | 1              | 1           |

| 0              | 0     | 1     | 0     | 0              | 0       | 1     | 0              | 2           |

| 0              | 0     | 1     | 1     | 0              | 0       | 1     | 1              | 2<br>3<br>4 |

| 0              | 1     | 0     | 0     | 0              | 1       | 0     | 0              | 4           |

| 0              | 1     | 0     | 1     | 1              | 0       | 1     | 1              | 5           |

| 0              | 1     | 1     | 0     | 1              | 1       | 0     | 0              | 6           |

| 0              | 1     | 1     | 1     | 1              | 1       | 0     | 1              | 7           |

| 1              | 0     | 0     | 0     | 1              | 1       | 1     | 0              | 8           |

| 1              | 0     | 0     | 1     | 1              | 1       | 1     | 1              | 9           |

| 1              | 0     | 1     | 0     | ×              | ×       | ×     | ×              |             |

| 1              | 0     | 1     | 1     | ×              | ×       | ×     | ×              |             |

| 1              | 1     | 0     | 0     | ×              | ×       | ×     | ×              |             |

| 1              | 1     | 0     | 1     | ×              | ×       | ×     | ×              |             |

| 1              | 1     | 1     | 0     | ×              | ×       | ×     | ×              |             |

| 1              | 1     | 1     | 1     | ×              | ×       | ×     | ×              |             |

|                |       |       |       |                |         |       |                |             |

At the rising edge of the First clock pulse the content of location  $(0110)_2 = 6 \Rightarrow 1010$ appears on the data bus, at the rising of the second clock pulse the content of location  $(1010)_2 = 10_2 \Rightarrow 1000$  appears on the data bus.

# 05. Ans: (b)

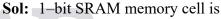

In 2 Inverters, output of the  $1^{st}$  Inverter is connected to Gate Input of  $2^{nd}$  Inverter and vice versa.

# A/D & D/A Converters

# Chapter

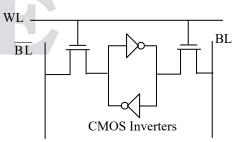

### 01. Ans: (b)

Sol:

| CLK | Co             | un | ter  | D | eco | der               | •                | V <sub>0</sub> |   |

|-----|----------------|----|------|---|-----|-------------------|------------------|----------------|---|

|     | $\mathbf{Q}_2$ | Q  | 1 Q0 | D | 3 D | $_2 \mathbf{D}_1$ | $\mathbf{D}_{0}$ |                |   |

| 1   | 0              | 0  | 0    | 0 | 0   | 0                 | 0                | 0              |   |

| 2   | 0              | 0  | 1    | 0 | 0   | 0                 | 1                | 1              |   |

| 3   | 0              | 1  | 0    | 0 | 0   | 1                 | 0                | 2              |   |

| 4   | 0              | 1  | 1    | 0 | 0   | 1                 | 1                | 3              | y |

| 5   | 1              | 0  | 0    | 1 | 0   | 0                 | 0                | 8              |   |

| 6   | 1              | 0  | 1    | 1 | 0   | 0                 | 1                | 9              |   |

| 7   | 1              | 1  | 0    | 1 | 0   | 1                 | 0                | 10             |   |

| 8   | 1              | 1  | 1    | 1 | 0   | 1                 | 1                | 10             |   |

Sol: -11111-

R

R

R

\*\*\*/

2R

$$R_{equ} = (((((2R||2R)+R)||2R)+R)||2R) + R)||2R)$$

$$R_{equ} = R = 10k\Omega.$$

$I = \frac{V_R}{R} = \frac{10V}{10k} = 1mA.$

Current division at  $\frac{1}{16}$

$$=\frac{1\times10^{-3}}{16}=62.5\,\mu\,A$$

# 03. Ans: (c)

Sol: Net current at inverting terminal,

$I_i = \frac{I}{4} + \frac{I}{16} = \frac{5I}{16}$

$$V_0 = -I_i R = -\frac{5I}{16} \times 10k\Omega$$

$$= \frac{-5 \times 1 \times 10^{-3} \times 10 \times 10^3}{16} = -3.125V$$

# 04. Ans: (d)

Sol: Given that

$$V_{DAC} = \sum_{n=0}^{3} 2^{n-1} b_n$$

Volts

$V_{DAC} = 2^{-1} b_0 + 2^0 b_1 + 2^1 b_2 + 2^2 b_3$

$\Rightarrow V_{DAC} = 0.5b_0 + b_1 + 2b_2 + 4b_3$

Initially counter is in 0000 state

|    | Up                                                                                      | V <sub>DAC</sub> (V) | o/p of     |

|----|-----------------------------------------------------------------------------------------|----------------------|------------|

|    | counter o/p                                                                             |                      | comparator |

|    | <b>b</b> <sub>3</sub> <b>b</b> <sub>2</sub> <b>b</b> <sub>1</sub> <b>b</b> <sub>0</sub> |                      |            |

|    | 0 0 0 0                                                                                 | 0                    | 1          |

|    | 0 0 0 1                                                                                 | 0.5                  | 1          |

|    | 0 0 1 0                                                                                 | 1                    | 1          |

|    | 0 0 1 1                                                                                 | 1.5                  | 1          |

|    | 0 1 0 0                                                                                 | 2                    | 1          |

|    | 0 1 0 1                                                                                 | 2.5                  | 1          |

| 25 | 0 1 1 0                                                                                 | 3                    | 1          |

|    | 0 1 1 1                                                                                 | 3.5                  | 1          |

|    | 1 0 0 0                                                                                 | 4                    | 1          |

|    | 1 0 0 1                                                                                 | 4.5                  | 1          |

|    | 1 0 1 0                                                                                 | 5                    | 1          |

|    | 1 0 1 1                                                                                 | 5.5                  | 1          |

|    | 1 1 0 0                                                                                 | 6                    | 1          |

|    | 1 1 0 1                                                                                 | 6.5                  | 0          |

When  $V_{DAC} = 6.5$  V, the o/p of comparator is '0'. At this instant, the clock pulses to the counter are stopped and the counter remains in 1101 state.

... The stable reading of the LED display is 13.

# Architecture, Pin Details of 8085 & Interfacing with 8085

Chapter

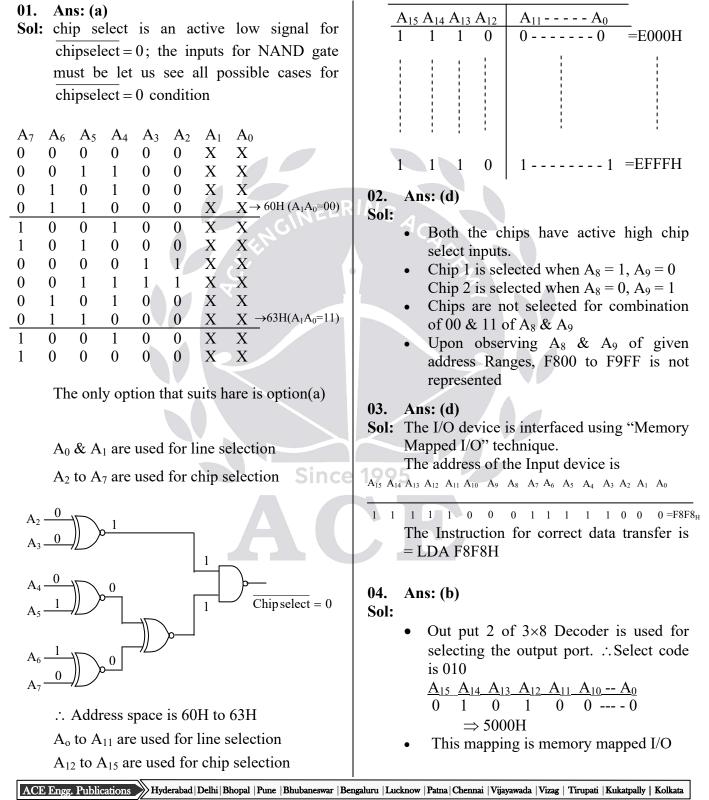

To provide cs as low, The condition is

$A_{15} = A_{14} = 0$  and  $A_{13} A_{12} = 01$  (or) (10)

i.e  $A_{15} = A_{14} = 0$  and  $A_{13} A_{12}$  shouldn't be 00, 11.

Thus it is  $A_{15} + A_{14} + [A_{13}A_{12} + \overline{A_{13}}, \overline{A_{12}}]$

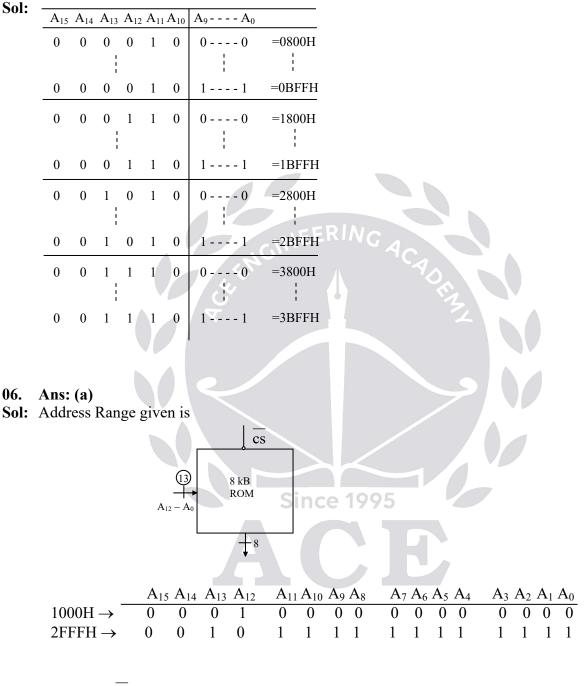

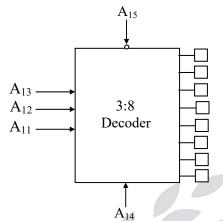

07. Ans: (a) Sol:

A<sub>15</sub>, A<sub>14</sub> are used for chip selection

A13, A12, A11 are used for input of decoder

| A <sub>15</sub> A <sub>14</sub> | A <sub>13</sub> A <sub>12</sub> A <sub>11</sub> | $A_{10}$ $A_0$ |

|---------------------------------|-------------------------------------------------|----------------|

| Enable of                       | Input of decoder                                | Address of     |

| decoder                         |                                                 | chip           |

Size of each memory block =  $2^{11} = 2K$

ACE Engg. Publications Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Bengaluru | Lucknow | Patna | Chennai | Vijayawada | Vizag | Tirupati | Kukatpally | Kolkata

Since 1995

# Lhapter **10** *Instruction set of 8085 & Programming with 8085*

| 01.<br>Sol: | Ans: (c)<br>6010H : LXI H,8A79H ; (HL) = 8A79H<br>$6013H : MOV A, L ; (A) \leftarrow (L) = 79$<br>6014H : ADD H ; (A) = 0111 1001<br>+<br>; (H) = 1000 1010<br>; (A) = 0000 0011<br>CY = 1, AC = 1<br>6015H : DAA<br>; 66 Added to (A)<br>since CY=1 &<br>AC = 1                                                                                                       | 04.<br>Sol: | RET → returned to the main program<br>∴ The contents of Accumulator after<br>execution of the above SUB2 is 02H<br>Ans: (c)<br>The loop will be executed until the value in<br>register equals to zero, then,<br>Execution time<br>=9(7T+4T+4T+10T)+(7T+4T+4T+7T)+7T<br>= 254T                                                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02.<br>Sol: | ; (A) = 69H<br>6016H : MOV H,A ; (H) $\leftarrow$ (A) =69H<br>6017H : PCHL ; (PC) $\leftarrow$ (HL) = 6979H<br><b>Ans: (c)</b><br>0100H : LXI SP, 00FFH ; (SP) = 00FFH<br>0103H : LXI H, 0107 H ; (HL) = 0107H<br>0106H : MVI A, 20H ; (A) = 20H<br>0108H : SUB M ; (A) $\leftarrow$ (A)-(0107)<br>; (0107) = 20H<br>; (A) = 00H<br>The contents of Accumulator is 00H | <b>→</b>    | Ans: (d)<br>H=255 : L = 255, 254, 253,0<br>H=254 : L = 0, 255, 254,0<br>H=1 : L = 0, 255, 254, 253,0<br>H=0 :<br>In first iteration (with H=255), the value in<br>L is decremented from 255 to 0 i.e., 255<br>times<br>In further remaining 254 iterations, the<br>value in L is decremented from 0 to 0 i.e.,<br>256 times<br>$\therefore$ 'DCRL' instruction gets executed for<br>$\Rightarrow [255 + (254 \times 256)]$<br>$\Rightarrow 65279$ times |

| 03.<br>Sol: | Ans: (c)<br>SUB1 : MVI A, 00H $A \leftarrow 00H$<br>CALL SUB2 $\rightarrow$ program will shifted to<br>SUB 2 address location<br>SUB 2 : INR $A \rightarrow A$<br>01H                                                                                                                                                                                                  | 06.<br>Sol: | <b>Ans: (a)</b><br>"STA 1234H" is a 3-Byte Instruction and it<br>requires 4 Machine cycles (Opcode fetch,<br>Operand1 Read, Operand2 Read, Memory<br>write). The Higher order Address (A <sub>15</sub> – A <sub>8</sub> )<br>sent in 4 machine cycles is as follows<br>Given "STA 1234" is stored at 1FFEH                                                                                                                                              |

i.e., Address Instruction

# 1FFE, 1FFF, 2000 : STA 1234H

| Machine<br>cycle    | Address<br>(A <sub>15</sub> -A <sub>0</sub> ) | Higher order<br>address<br>(A <sub>15</sub> -A <sub>8</sub> ) |

|---------------------|-----------------------------------------------|---------------------------------------------------------------|

| 1. Opcode<br>fetch  | 1FFEH                                         | 1FH                                                           |

| 2. Operand1<br>Read | 1FFFH                                         | 1FH                                                           |

| 3. Operand2<br>Read | 2000H                                         | 20Н                                                           |

| 4. Memory<br>Write  | 1234H                                         | 12H                                                           |

i.e. Higher order Address sent on A15-A8 for

4 Machine Cycles are 1FH, 1FH, 20H, 12H.

### 07. Ans: (d)

Sol: The operation SBI **BE**<sub>H</sub> indicates  $A-BE \rightarrow A$  where A indicates accumulator Thus the result of the subtraction operation is stored in the accumulator and the contents of accumulator are changed.

### **08.** Ans: (c)

Sol: If the content in register B is to be multiplied with the content in register C, the contents of register B is added to the accumulator (initial value of accumulator is 0) for C times.