Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Bengaluru | Lucknow Patna | Chennai | Vijayawada | Vizag | Tirupathi | Kukatpally | Kolkata

**ACE** Engineering Academy has taken utmost care in preparing the **ESE-2018** Mains Examination solutions. Discrepancies, if any, may please be brought to our notice. **ACE** Engineering Academy do not owe any responsibility for any damage or loss to any person on account of error or omission in these solutions. **ACE** Engineering Academy is always in the fore front of serving the students, irrespective of the examination type (GATE/ESE/PSUs/PSC/GENCO/TRANSCO etc.,).

All Queries related to ESE - 2018 Mains Solutions are to be sent to the following email address hyderabad@aceenggacademy.com | Contact Us : **040 - 23234418, 19, 20**

#### **PAPER REVIEW**

Paper was overall moderate, material science, measurements and mathematics had some questions from our test series. Networks questions are direct and easy. EMTL questions are direct previous years. Some one, who followed ACE test series, feels the paper really easy. Section-B is relatively tougher than section-A and the paper is lengthy.

| SUBJECT(S)                             | LEVEL    | Marks |

|----------------------------------------|----------|-------|

|                                        |          |       |

| Engineering Mathematics                | Easy     | 72    |

| Electric Circuits and Fields           | Easy     | 84    |

| Basic Electronics Engineering          | Hard     | 84    |

| Electrical and Electronic Measurements | Moderate | 72    |

| Electrical Materials                   | Moderate | 84    |

| Computer Fundamentals                  | Hard     | 84    |

#### **SUBJECT WISE REVIEW**

Subject Experts, ACE Engineering Academy

#### **SECTION – A**

01. (a) Let

$$\mathbf{A} = \begin{bmatrix} 5 & -2 & 0 \\ -2 & 6 & 2 \\ 0 & 2 & 7 \end{bmatrix}$$

and  $\mathbf{B} = \mathbf{A}^3 - 2\mathbf{A}^2 - 5\mathbf{A} + 6\mathbf{I}$ ,

Where I is the identity matrix, then calculate the determinant of B.

(12M)

Sol:

Given, A =  $\begin{bmatrix} 5 & -2 & 0 \\ -2 & 6 & 2 \\ 0 & 2 & 7 \end{bmatrix}$

Characteristic equation of A is  $|A - \lambda I| = 0$

$$\Rightarrow \begin{bmatrix} 5-\lambda & -2 & 0 \\ -2 & 6-\lambda & 2 \\ 0 & 2 & 7-\lambda \end{bmatrix} = 0$$

By expanding

$$\lambda^3 - 18\lambda^2 + 99\lambda - 162 = 0$$

$$\Rightarrow (\lambda - 3)(\lambda^2 - 15\lambda + 54) = 0$$

$$\Rightarrow (\lambda - 3)(\lambda - 9)(\lambda - 6) = 0$$

Eigen values of A are 3, 9, 6.

For  $B = A^3 - 2A^2 - 5A + 6I$  eigen values corresponding to

$$3 \rightarrow 27 - 18 - 15 + 6 = 0$$

$9 \rightarrow 729 - 162 - 45 + 6 = 528$

$$6 \rightarrow 216 - 72 - 30 + 6 = 120$$

We know that determinant of A matrix is equal to product of eigen values

$$|\mathbf{B}| = 0 \times 528 \times 120$$

An infinite number of charges each equal to q Coulombs' are placed in a free space along the line at x = 1, x = 2, x = 4, x = 8, x = 16 and so on. Find the expression for potential and electric field intensity at point x = 0, due to these systems of charges. Assume that values of x are in metres. (12M)

Sol:

Resultant potential at the origin is

37.1

$$V_{T} = \frac{q}{4\pi\varepsilon_{0}} \sum_{i=1}^{\infty} \frac{1}{r} \text{ as this}$$

$$= \frac{q}{4\pi\varepsilon_{0}} \left[ \underbrace{1 + \frac{1}{2} + \frac{1}{4} + \frac{1}{8} \dots}_{G,P} \right]$$

$$= \frac{q}{4\pi\varepsilon_{0}} \left[ \underbrace{\frac{a}{1-r}}_{1-r} \right], r = \frac{1}{2}, a = 1$$

$$V_{T} = \frac{q}{4\pi\varepsilon_{0}} \cdot \frac{1}{1 - \frac{1}{2}}$$

$$\therefore V_{T} = \frac{q}{4\pi\varepsilon_{0}} \cdot \frac{1}{1 - \frac{1}{2}}$$

$$\therefore V_{T} = \frac{q}{4\pi\varepsilon_{0}} \sum_{i=1}^{\infty} \frac{1}{r_{i}^{2}} \Rightarrow \frac{q}{4\pi\varepsilon_{0}} \left[ 1 + \frac{1}{4} + \frac{1}{16} + \frac{1}{64} + \dots \right] (-\hat{a}_{x})$$

$$= \frac{q}{4\pi\varepsilon_{0}} \left[ \frac{1}{1 - \frac{1}{4}} \right] (-\hat{a}_{x}) = \frac{Q}{4\pi\varepsilon_{0}} \times \frac{4}{3} (-\hat{a}_{x})$$

$$\therefore E_{T} = \frac{Q}{3\pi\varepsilon_{0}} (-\hat{a}_{x}) V/m$$

:5:

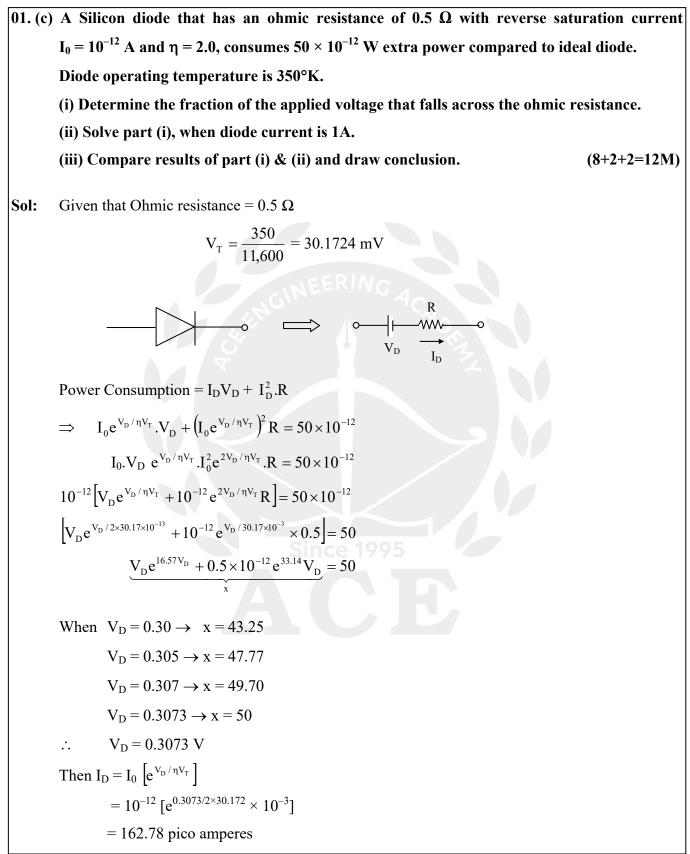

= 2.1673 W

As diode current becomes 1 A,  $V_D = 1.6673$  and power consumes 2.1673 W

$\Rightarrow$  For change in current of 162.78 PA to 1 A the voltage across diode changes from 0.3073 to 1.6673 V

For a large change in current there is a small change in voltage. So diode is a logarithmic device (non linear device).

:6:

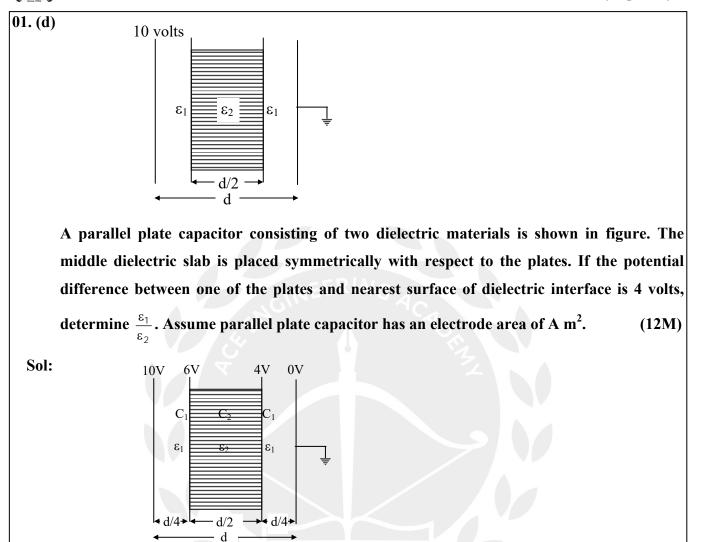

In this all the three dielectrics are connected in series. So, the charge is same through the dielectrics, i.e.,  $Q_1 = Q_2$

Generally capacitance,

$$C = \frac{\varepsilon A}{d}$$

$C_1 = \frac{\varepsilon_0 \varepsilon_1 \times A}{d/4} = \frac{4\varepsilon_0 \varepsilon_1 \times A}{d}$

Similarly,  $C_2 = \frac{\varepsilon_0 \varepsilon_2 A}{d/2} = -\frac{2\varepsilon_0 \varepsilon_2 A}{d}$

$C_1 V_1 = C_2 V_2$

$\frac{4\varepsilon_0 \varepsilon_1 A}{d} \times 4 = \frac{2\varepsilon_0 \varepsilon_2 A}{d} \times 2$

$\frac{\varepsilon_1}{\varepsilon_2} = \frac{1}{4}$

01. (e)

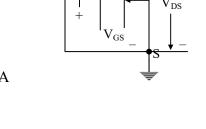

G G  $I_{DSS} = 5 \text{ mA}$   $V_p = -4V$

Write the equation related to the drain current  $(I_D)$  and Gate to source voltage  $V_{GS}$  explaining all the parameters for

(i) Depletion type MOSFET

(ii) Enhancement type MOSFET

(iii) Determine V<sub>DS</sub> for the circuit shown in the figure.

(4+4+4=12M)

#### Sol: (i) Depletion type MOSFET

Case (i) Cutoff region:

$I_D = 0 \dots (1)$

In this case  $V_{GS} = V_{GS(OFF)} = V_P \dots 1(a)$

Case (ii) Saturation region:

$$I_{D} = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_{P}} \right]^{2} \dots \dots (2) \text{ (Neglecting channel length modulation effect i.e } \lambda = 0)$$

Where I<sub>D</sub> is the total drain current in the device

I<sub>DSS</sub> is the drain to source current with the gate shorted to the source.

$V_{GS}$  is the reverse biased gate to source voltage, generally  $V_{GS}$  is negative for an N-channel MOSFET in Depletion Mode.

$V_P$  is the pinch-off voltage: The maximum reverse biased gate to source voltage at which the channel becomes pinched-off or becomes very low and the current through the channel becomes almost zero is called pinch-off voltage.

**NOTE:** I<sub>DSS</sub> is the device parameter, defined by manufacturer and is given by,

:7:

$I_{DSS} = \frac{1}{2} \mu_n C_{ox} V_{th}^2$  .....(3)

Where " $\mu_n C_{ox}$ " is know as process transconductance parameter in which  $\mu_n$  is the

mobility of electron  $C_{\text{ox}}$  oxide capacitance and  $V_{\text{th}}$  is the threshold voltage.

#### (ii) Enhancement MOSFET:

Case (i) Cutoff Region:

$I_D = 0 \dots (1)$  in this case,  $V_{GS} \le V_P$ ;

Case (ii) Saturation region:

$$I_{\rm D} = \frac{1}{2} \mu_{\rm n} C_{\rm ox} \frac{W}{L} (V_{\rm GS} - V_{\rm th})^2 \dots (2)$$

Where,

$\mu_n$  = mobility of electron

$C_{ox} = Oxide \text{ capacitance} = \frac{\varepsilon_{ox}}{t_{ox}}$  (where  $\varepsilon_{ox}$  permitivity & silicon oxide  $t_{ox}$  is oxide

thickness)

(**NOTE:** ' $\mu_n C_{ox}$ ' is known as process trans conductance parameter)

W = channel width

$$\left[ \text{Generally } \frac{W}{L} \text{ is known as aspect ratio of the MOSFET} \right]$$

L = channel length

$V_{GS}$  = applied gate to-source voltage. Generally  $V_{GS}$  is positive in Enhancement mode of an N-channel MOSFET.

$V_{th}$  = Threshold voltage

(iii) Given  $I_{DSS} = 5 \text{ mA}$ ,  $V_p = -4V$ Step (1) From the circuit,

$$V_{GS} = OV$$

Step (2): consider shockly equation,

$$I_{\rm D} = I_{\rm DSS} \left[ 1 - \frac{V_{\rm GS}}{V_{\rm P}} \right]^2 = 5 \text{mA} \left[ 1 - \frac{0}{-4V} \right] = 4 \text{mA}$$

Step (3): KVL for output section,

$20V - I_D R_D - V_{DS} = 0$   $\Rightarrow V_{DS} = 20V - I_D R_D$ Let  $R_D = 3k\Omega$  $\therefore V_{DS} = 20V - 5mA \times 3k\Omega = 5V$

02. (a) Show that in the interval (0, 1)

$$\cos \pi x = \frac{8}{\pi} \sum_{n=1}^{\infty} \frac{n}{4n^2 - 1} \cdot \sin 2n\pi x$$

**Sol:**  $f(x) = \cos \pi x$

Half range sine series of f(x) in the interval (-1, 1)

Where  $b_n = 2 \int_0^1 f(x) \sin n\pi x \, dx$

$b_n = 2\int_0^1 \cos \pi x . \sin n\pi x ... dx$

$$\mathbf{b}_{n} = \int_{0}^{1} \left[ \sin(n\pi \mathbf{x} + \pi \mathbf{x}) + \sin(n\pi \mathbf{x} - \pi \mathbf{x}) \right] d\mathbf{x}$$

$$\begin{split} b_{n} &= \left[\frac{-\cos(n+1)\pi x}{(n+1)\pi}\right]_{0}^{1} + \left[\frac{-\cos(n-1)\pi x}{(n-1)\pi}\right]_{0}^{1} \\ b_{n} &= \left[\frac{(-1)^{n}}{(n+1)\pi} + \frac{(-1)^{n}}{(n-1)\pi}\right] + \left[\frac{1}{(n+1)\pi} + \frac{1}{(n-1)\pi}\right] \\ &= \frac{(-1)^{n}}{\pi} \left[\frac{2n}{n^{2}-1}\right] + \frac{1}{\pi} \left[\frac{2n}{n^{2}-1}\right] \text{ where } n = 1, 2, 3 \dots \dots \\ &= \frac{2n}{(n^{2}-1)\pi} \left[(-1)^{n} + 1\right] \\ &= \frac{4n}{(n^{2}-1)\pi} \qquad \text{if } n = \text{even} \\ &= 0 \qquad \qquad \text{if } n = \text{odd} \end{split}$$

(20M)

$$=\frac{4(2m)}{(4m^2-1)\pi}\dots(2)$$

...(2) where m = 1, 2, 3....

Sub (2) in (1) then

$$f(x) = \sum_{m=1}^{\infty} \frac{8m}{(4m^2 - 1)\pi} \sin(2m\pi x)$$

$$f(x) = \frac{8}{\pi} \sum_{n=1}^{\infty} \frac{n}{(4n^2 - 1)} \sin(2n\pi x)$$

(∵m is dummy variable)

# G.S. ENGG. APTITUDE BATCH DESE - 2019 1<sup>st</sup> JULY @ DELHI START KARIY. GAIN SURFLY.

ACE Engg. Publications Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Bengaluru | Lucknow | Patna | Chennai | Vijayawada | Vizag | Tirupati | Kukatpally | Kolkata

Ŷ

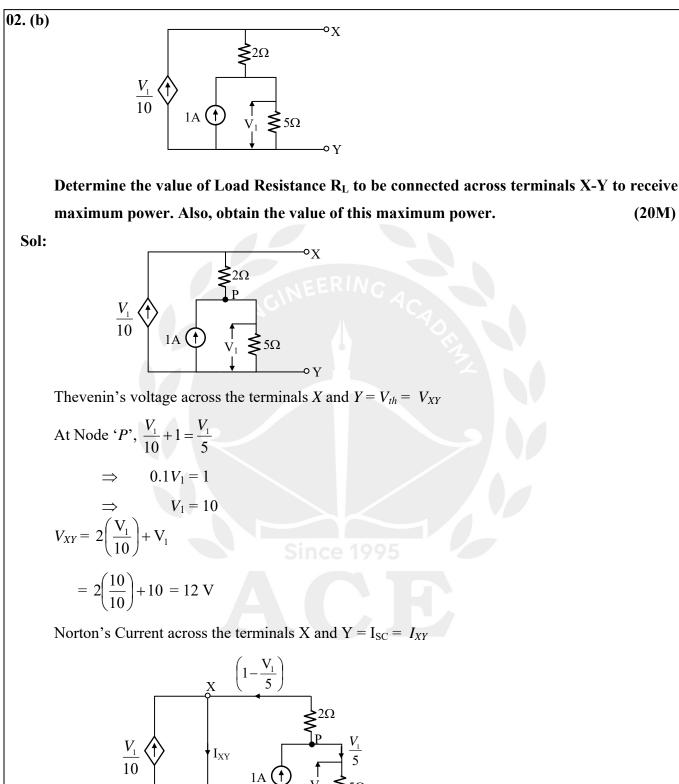

Thevenin's equivalent resistance

$$R_{th} = \frac{V_{sc}}{I_{sc}} = R_{XY} = \frac{V_{xY}}{I_{xY}} = \frac{12}{6/7} = 14 \ \Omega$$

Thevenin's equivalent circuit across terminals XY:

The value of load resistance connected across terminals for max power transfer

$$R_{XY} = R_{th} = R_L = 14 \ \Omega$$

Maximum power deliver to the load  $R_L = \frac{V_{XY}^2}{4R_{XY}} = \frac{12^2}{4 \times 14} = \frac{144}{56} = 2.571 \text{ W}$

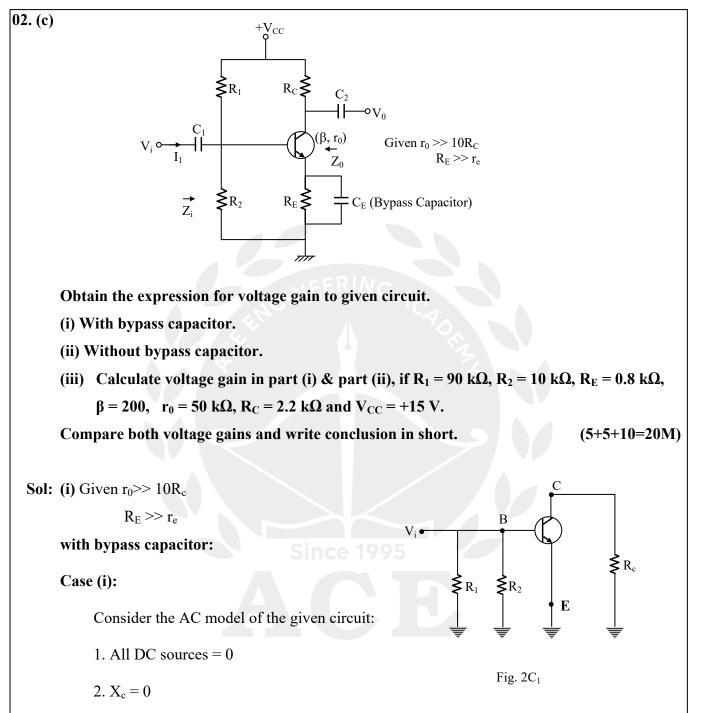

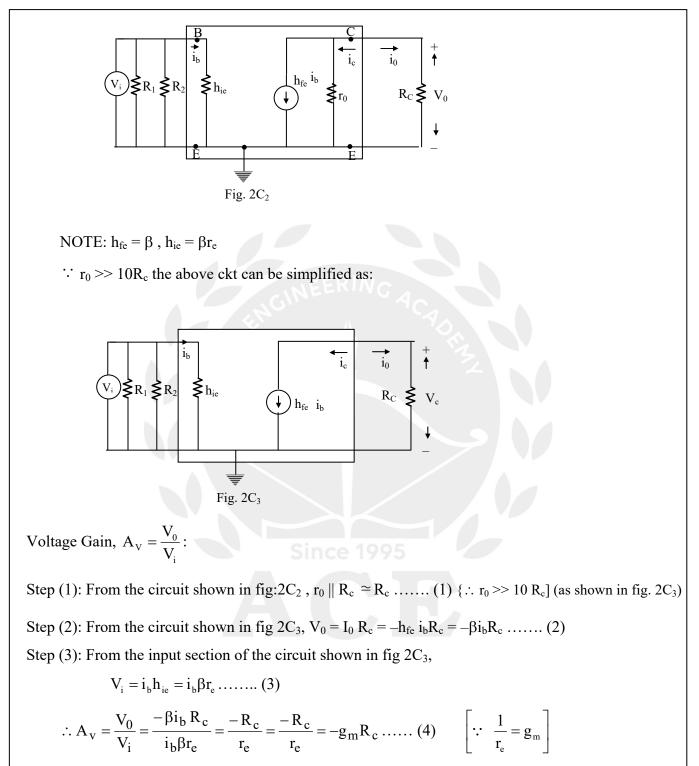

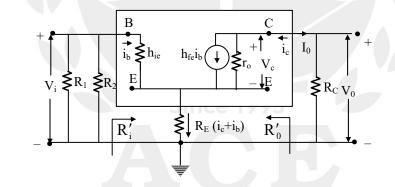

**Case (ii):** small signal model of the amplifier shown in fig. $2C_1$

$$=\frac{-h_{fe}R_{c}}{h_{ie}}\dots\dots(5) \quad \because \quad g_{m}=\frac{h_{fe}}{h_{ie}}$$

NOTE: If

$$\beta$$

is large,  $A_V = \frac{-R_c}{R_E} \dots (7)$

(iii) Given  $R_1 = 90k\Omega$ ,  $R_2 = 10k\Omega$ ,  $R_E = 0.8k\Omega$ ,  $\beta = 200$ ,  $r_0 = 50 k\Omega$ ,  $R_c = 2.2 k\Omega$  and  $V_{cc} = 15V$

Part (i): CE amplifier with bypass capacitor:

$$A_{V} = \frac{-h_{fe}(R_{c} || r_{0})}{h_{ie}} = -g_{m}(R_{c} || r_{0}).....(1) \left[ \because \frac{h_{fe}}{h_{ie}} = g_{m} \right]$$

Case (i): Consider the DC model of the given circuit:

- 1. All AC source = 0

- 2.  $X_c = \infty$

Step (1):

$$V_{th} = \frac{R_2(V_{cc})}{R_1 + R_2} = \frac{10k(15V)}{90k + 10k} = 1.5V = V_B \dots (1) [::\beta \text{ isl arg e}]$$

Step (2) : KVL for B-E loop of B.J.T:

$$V_{th} - V_{BE} - I_E R_E = 0.....(2)$$

$$\Rightarrow I_E = \frac{V_{Th} - V_{BE}}{R_E} = \frac{1.5V - 0.7V}{0.8k\Omega} = 1mA.....(3)$$

$$\therefore g_m = \frac{1}{r} = \frac{I_E}{V_{-}} = \frac{1mA}{26mV} = 0.03846 \text{ mho}.....(4)$$

$$R_{1} = R_{C}$$

$$R_{1} = R_{C}$$

$$R_{1} = R_{C}$$

$$R_{1} = R_{C}$$

$$R_{L} = R_{C}$$

$$R_{L} = R_{C}$$

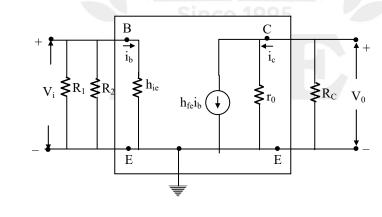

Case (ii): Consider the small signal model

Step (i):

$$V_0 = -h_{fe}i_b(r_o || R_c)....(1)$$

$V_i = i_b h_{ie} ....(2)$

Step (ii):

$$A_{V} = \frac{V_{0}}{V_{i}} = \frac{-h_{fe}i_{b}(r_{0} || R_{c})}{i_{b}} \dots (3)$$

$$= \frac{-h_{fe}(r_{0} || R_{c})}{h_{ie}} \dots (4)$$

$$= -g_{m} (r_{0} || R_{c}) \dots (5)$$

$$= -0.03846 \ \forall [50k||2.2k] \dots (6)$$

$$\therefore A_{v} = -81.045977 \dots (7)$$

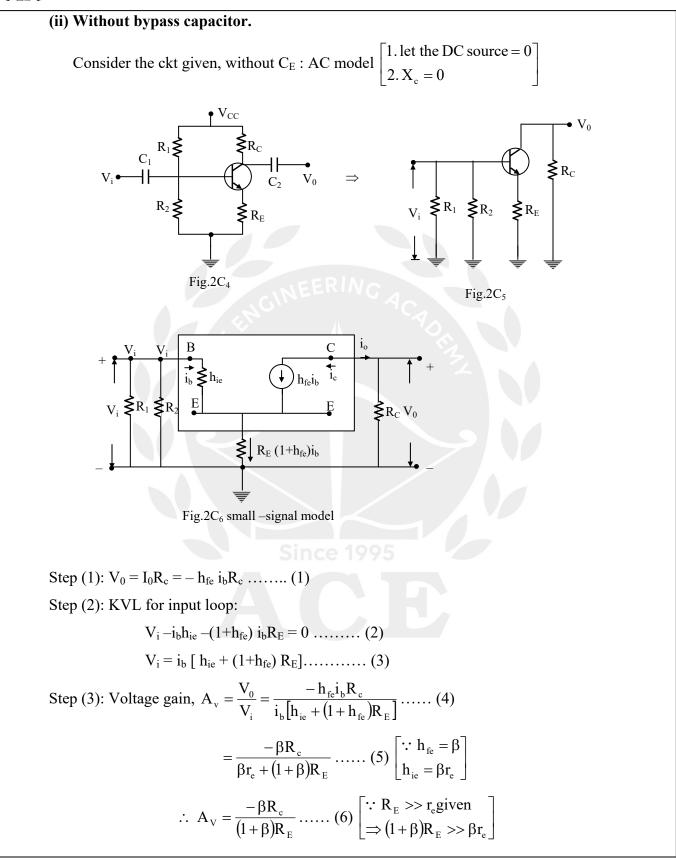

Part(ii) CE Amplifier without CE:

Case (i) : same as part(i)

$$I_{E} = 1mA \dots (1)$$

$$\Rightarrow r_{e} = \frac{V_{T}}{I_{E}} = \frac{26mV}{1mA} = 26\Omega \dots (2)$$

#### **Approximate Approach:**

Case (ii) given  $r_0 50k \& R_c = 2.2.k$

$:: r_0 >> R_c$  (i.e  $r_0 >> 10R_c$ ), the simplified small -signal model can be shown as follows

$$+ \underbrace{R_1}_{V_i} = \underbrace{R_1}_{R_2} \underbrace{R_2}_{R_E} \underbrace{R_E}_{R_E} \underbrace{R_C}_{R_E} \underbrace{V_0}_{R_E} \underbrace{V_0} \underbrace{V_0}_{R_E} \underbrace{V_0} \underbrace{V_0}$$

Step(1):  $V_0 = I_0 R_C = -h_{fe} i_b R_c$  .....(1)

Step(2) : KVL for input loop

$$V_{i} - i_{b}h_{ie} - i_{b} (1+h_{fe}) R_{E} = 0 \dots (2)$$

$$\Rightarrow V_{i} = i_{b} [h_{ie} + (1+h_{fe}) R_{E}] \dots (3)$$

Step(3):

$$A_{V} = \frac{V_{0}}{V_{i}} = \frac{-h_{fe}i_{b}R_{c}}{i_{b}[h_{ie} + (1 + h_{fe})R_{E}]}$$

....(4)

#### **Comparison:**

Case (i):  $A_V = -81.045977$  [with by pass capacitor]

Case (ii):  $A_V = -2.65$  [without by pass capacitor]

NOTE: In a CE amplifier, if the bypass capacitor is open, the voltage gain,  $A_V$  decreases, because the unbypassed  $R_E$  causes negative feed back.

#### This problem can be solved more accurately with the following approach:

#### Accurate Approach:

Case (ii): Small –signal model

Step (1):

$$R'_{i} = h_{ie} + \left[ \frac{(1+h_{fe}) + \frac{R_{c}}{r_{0}}}{1+(\frac{R_{c}+R_{E}}{r_{0}})} \right] R_{E} \dots \dots (1)$$

=  $\beta r_{e} + \left[ \frac{(1+\beta) + \frac{R_{c}}{r_{0}}}{1+(\frac{R_{c}+R_{E}}{r_{0}})} \right] R_{E} \dots \dots (2)$

$$:: \frac{R_{C}}{r_{0}} = \frac{2.2k}{50k} = 0.044 <<(1+\beta),$$

$$R'_{i} = \beta r_{e} + \left[\frac{(1+\beta)}{1+(\frac{R_{c}+R_{E}}{r_{0}})}\right] R_{E} \dots (3)$$

$$: r_{0} > 10(R_{c}+R_{E}), \frac{R_{c}+R_{E}}{r_{0}} <<1 \dots (4)$$

$$R'_{i} = \beta r_{e} + (1+\beta)R_{E} \dots (5)$$

$$: V_{i} = i_{b}R'_{i} = i_{b}[\beta r_{e} + (1+\beta)R_{E}] \dots (6)$$

$$Step (2): R'_{0} = r_{0} + \frac{h_{E}r_{0} + h_{E}}{1+\frac{h_{E}}{R_{E}}} \dots (7)$$

$$= r_{0} + \frac{\beta r_{0} + \beta r_{e}}{1+\frac{\beta r_{e}}{R_{E}}} \dots (9) [: r_{0} >> r_{e}]$$

$$= r_{0} \left[1 + \frac{\beta}{1+\frac{\beta r_{e}}{R_{E}}}\right] \dots (10)$$

$$= r_{0} \left[1 + \frac{200}{1+\frac{5.2}{0.8}}\right] \dots (11)$$

$$= r_{0} \left[1 + \frac{200}{6.5}\right] \dots (12)$$

$$: R'_{0} = 31.77r_{0} \dots (13)$$

$$Step (3): V_{0} = -i_{C}R'_{C} || R_{C} = -i_{C}R_{C} || 31.77r_{0} \dots (14)$$

$$= -i_{c}R_{c} \dots (15) [ \because 31.77r_{0} >> R_{c}]$$

$$= -h_{fe} i_{b} R_{c} \dots (16)$$

Step (4):  $A_{V} = \frac{V_{0}}{V_{i}} = \frac{-h_{fe}i_{b}R_{c}}{i_{b}(\beta r_{e} + (1+\beta)R_{E})} = \frac{-\beta R_{C}}{\beta r_{e} + (1+\beta)R_{E}} \dots (17)$

$$= \frac{200 \times 2.2k}{200 \times 26.2 + 201 \times 0.8k} \dots (18)$$

$$\therefore A_{V} = \frac{-440}{166} = -2.65 \dots (19)$$

03. (a) Evaluate

$$\oint_{C} \frac{z^2 + 4z + 8}{\left(z - \frac{1}{2}\right)^2 \left(z^2 + 2z + 5\right)} dz$$

where C is the contour  $|z + 1 - i| = 2$  in anti-clockwise

sense.

Sol:

$$\oint_C \frac{Z^2 + 4Z + 8}{\left(Z - \frac{1}{2}\right)^2 \left(Z^2 + 2Z + 5\right)}, \qquad |Z + 1 - i| = 2$$

Case (1):

For

$$Z_1 = \frac{1}{2}$$

,  $\Rightarrow 1\frac{1}{2} + 1 - i1 = 1.8 < 2$

$$\therefore$$

$Z_1 = \frac{1}{2}$  lies inside the contour

$$\oint_{C} \frac{f(Z)}{(Z-a)^{n}} = \frac{2\pi i}{(n-1)!} \operatorname{Lt}_{Z\to a} f^{n-1}(Z)$$

$$\therefore \quad \text{For } Z = \frac{1}{2}$$

$$f(Z) = \frac{Z^2 + 4Z + 8}{Z^2 + 2Z + 5}$$

$$\oint_{C} \frac{\frac{Z^{2} + 4Z + 8}{Z^{2} + 2Z + 5}}{\left(Z - \frac{1}{2}\right)^{2}} = \frac{2\pi i}{(2 - 1)!} \operatorname{Lt}_{Z \to \frac{1}{2}} f^{2 - 1}(Z)$$

ACE Engg, Publications Hyderabad | Delhi | Bhopal | Pune | Bhubaneswar | Bengaluru | Lucknow | Patna | Chennai | Vijayawada | Vizag | Tirupati | Kukatpally | Kolkata

(20M)

$$= 2\pi i \underbrace{Lt}_{z+\frac{1}{2}} f'(Z)$$

$$= 2\pi i \times Lt}_{z+\frac{1}{2}} \frac{(Z^2 + 2Z + 5)(2Z + 4) - (Z^2 + 4Z + 8)(2Z + 2)}{Z^2 + 2Z + 5)^2}$$

$$= 2\pi i \times \frac{Lt}{z+\frac{1}{2}} \frac{-2Z^2 - 6Z + 4}{(\frac{1}{4} + 2x\frac{1}{2} + 5)^2}$$

$$= 2\pi i \times \frac{-2x \frac{1}{4} - 6x \frac{1}{2} + 4}{(\frac{1}{4} + 2x \frac{1}{2} + 5)^2}$$

$$= 2\pi i \times \left(\frac{0.5}{39.0625}\right) = 0.08i$$

Case (2):

$$Z^2 + 2Z + 5 = (Z + 1 + 2i)(Z + 1 - 2i)$$

$$Z_2 = -1 - 2i \text{ lies outside the contour}$$

$$Z_3 = -1 + 2i, \Rightarrow |-1 + 2i + 1 - i| = 1 < 2$$

$$\therefore \text{ Lies inside the contour.}$$

For  $Z_3 = -1 + 2i$

$$= 2\pi i \underbrace{\frac{Z^2 + 4Z + 8}{(Z - \frac{1}{2})^2(Z + 1 + 2i)(Z + 1 - 2i)} \times (Z + 1 - 2i)}_{(Z - \frac{1}{2})^2(Z + 1 - 2i)(Z + 1 - 2i)}$$

$$= 2\pi i \underbrace{\frac{(-1 + 2i)^2 + 4(-1 + 2i) + 8}{(Z - \frac{1}{2})^2(-1 + 2i + 1 + 2i)}}_{= 2\pi i \times \frac{(-1 + 2i)^2 + 4(-1 + 2i) + 8}{(-1 + 2i - \frac{1}{2})^2(-1 + 2i + 1 + 2i)}}_{= 2\pi i \times \frac{\left[\frac{1 - 4 - 4i + 8i - 4 + 8}{(-4 + \frac{4}{4} - 6i)(4i)}\right]}_{= 2\pi i \times \left[\frac{1 - 4i}{(-7i + 24}\right] \times \frac{24 + 7i}{24 + 7i}}$$

$$-2\pi i \times \left(\frac{-4+103i}{625}\right)$$

$$-0.04i - 1.035$$

For,  $Z_2 = -1 - 2i$ ,  $\Rightarrow$  The contour integral is zero

$$\therefore \oint \frac{Z^2 + 4Z + 8}{\left(Z - \frac{1}{2}\right)^2 \left(Z^2 + 2Z + 5\right)} = Z_1 + Z_2 + Z_3$$

$$= 0.08i + 0 - 0.04i - 1.035$$

$$= 0.04i - 1.035$$

Model Questions asked in ACE ESE mains 2018 Test Series Mock-1, Q5(c).

(3. (b)

$$\frac{20}{v_1} - \frac{1}{1}i + \frac{1}{v_1} + \frac{1}{v_2}i + \frac{1}{v_1}i + \frac{1}{v_2}i + \frac{1}{v_2}i + \frac{1}{v_1}i + \frac{1}{v_1}i + \frac{1}{v_2}i + \frac{1}{v_2}i + \frac{1}{v_1}i + \frac{1}{v_2}i + \frac{1}{v_2}i + \frac{1}{v_1}i + \frac{1}{v_1}i + \frac{1}{v_2}i + \frac{1}{v_1}i +$$

$V_{S(rms)} = 24 \angle 0^{\circ} v, \omega = 100 \text{ rad/sec}$ Coefficient of coupling k = 1/3 $L_1 = 0.03 \text{ H}$  $X_{L1} = j\omega L_1 = j(100)(0.03) = j3 \Omega$ Mutual inductance,  $M = K \sqrt{L_1 L_2}$  $\Rightarrow X_M = K_{\sqrt{X_{L_1}X_{L_2}}}$  $=\frac{1}{3}\sqrt{(j3)(j3)}=j1 \ \Omega$ Apply KVL to 1<sup>st</sup> loop  $-V_S + 2I_1 + (j3 - j1)I_1 + (j1)I_2 = 0$  $V_S = (2 + 2j)I_1 + (j1)I_2 \dots (1)$ KVL to 2<sup>nd</sup> loop  $(2 + i3 - i2)I_2 + (i1)I_1 = 0$  $(j1)I_1 + (2+j1)I_2 = 0$  .....(2) (i) Writing the loop equations  $I_1$  and  $I_2$  in matrix form  $\begin{bmatrix} 24 \angle 0^{\circ} \\ 0 \end{bmatrix} = \begin{bmatrix} 2+2j & j1 \\ j1 & 2+j1 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}$

(ii) From the equation (2)

$(j1)I_1 + (2+j1)I_2 = 0$

$$\Rightarrow I_2 = \frac{-(j1)}{(2+j1)}I_1$$

Sub in (1) equation

$$V_{S} = (2+2j)I_{1} + (j1)I_{2}$$

$$= (2+2j)I_{1} + (j1) \times \frac{-(j1)}{(2+j1)}I_{1}$$

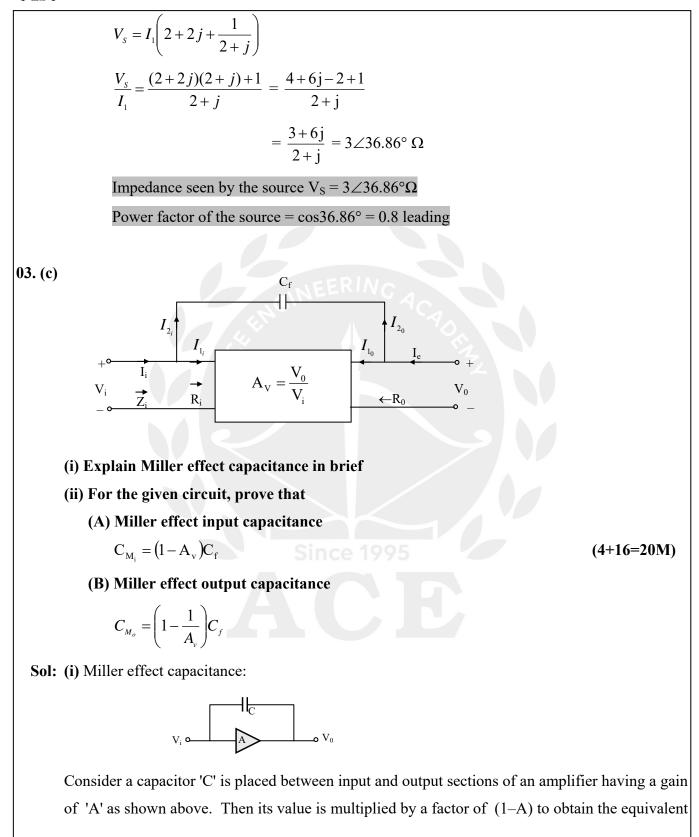

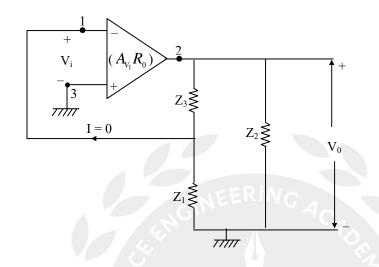

capacitance at the input side as shown in fig. The multiplication of a capacitor, C by a factor (1–A) is referred to as Miller effect or Miller multiplication

**NOTE:** The Miller effect capacitance cause significant effect on the high frequency response of BJT and FET amplifiers.

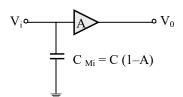

Consider the small signal model of a CE amplifier at High Frequencies

The upper 3 dB frequency of the amplifier shown in fig, is given by

$$f_{\rm H} = \frac{1}{2\pi r_{\rm be}' \left[ c_{\rm e} + c_{\rm c} \left( 1 + g_{\rm m} R_{\rm L}^{\rm 1} \right) \right]}$$

**Conclusion:** Due to the miller effect capacitor  $C_e(1 + g_m R'_L)$ , the upper 3-db frequency in CE amplifier is highly reduced.

(ii) Step(1): KVL from input to output

$$V_i - I_{2i} \frac{1}{sc_f} - V_0 = 0$$

$$\Rightarrow I_{2i} \cdot \frac{1}{sc_{f}} = v_{i} - V_{0}$$

$$= v_{i} \left[ 1 - \frac{V_{0}}{V_{i}} \right]$$

$$= V_{i} \left[ 1 - A_{v} \right]$$

$$\Rightarrow I_{2_{i}} = \frac{V_{i} \left[ 1 - A_{v} \right]}{\left( \frac{1}{sc_{f}} \right)}$$

$$\Rightarrow \frac{V_{i}}{I_{2_{i}}} = \frac{1}{j oc_{f} (1 - A_{v})} = \frac{1}{j oC_{Mi}}$$

$$\therefore C_{M} = \text{Miller effect input capacitan ce} = C_{f} [1 - A_{v}]$$

Step: (2): KVL from output to input

$$v_{0} - I_{2_{w}} \frac{1}{sc_{f}} - V_{i} = 0$$

$$\Rightarrow I_{2_{u}} \frac{1}{sc_{f}} = v_{0} - V_{i}$$

$$= v_{0} \left[ 1 - \frac{V_{i}}{V_{o}} \right]$$

$$= v_{0} \left[ 1 - \frac{1}{A_{v}} \right]$$

$$\Rightarrow \frac{V_{0}}{I_{2_{w}}} = \frac{1}{j oc_{f} \left( 1 - \frac{1}{A_{v}} \right)} = \frac{1}{j oc_{M_{w}}}$$

$$\therefore C_{M_{u}} = \text{Miller effect output capacitan ce} = C_{f} \left( 1 - \frac{1}{A_{v}} \right)$$

04. (a) Let the probability density function of a random variable X be given as:

$$f(x) = \frac{5}{3}e^{-5x}u(x) + \beta e^{2x}u(-x)$$

Where  $\beta$  is a constant and  $u(x)$  is the unit step function. Calculate:

(i) The value of  $\beta$

(ii) Mean of X

(iii) Variance of X (3+7+10 M)

Sol: Given,

Probability density function,  $f(x) = \frac{5}{3}e^{-5x}u(x) + \beta e^{2x}u(-x)$

$$\int_{-\infty}^{\infty} f(x)dx = 1$$

$$\int_{-\infty}^{0} \beta e^{2x}dx + \int_{0}^{\infty} \frac{5}{3}e^{-5x}dx = 1$$

$$\frac{\beta}{2}[e^{2x}]_{-x}^{n} + \frac{5}{3} \times \frac{1}{(-5)}[e^{-5x}]_{-x}^{n} = 1$$

$$\frac{\beta}{2}[e^{2x0} - e^{2x(-x)}] - \frac{1}{3}[e^{-5x-x} - e^{-5x0}] = 1$$

$$\frac{\beta}{2}[1-0] - \frac{1}{3}[0-1] = 1$$

$$\frac{\beta}{2} + \frac{1}{3} = 1$$

(i)  $\frac{\beta}{2} = \frac{2}{3} \Rightarrow \beta = \frac{4}{3}$

$$\therefore f(x) = \frac{5}{3}e^{-5x}d(x) + \frac{4}{3}e^{2x}d(-x)$$

(ii) Mean of  $X_{-x} = \int_{-\infty}^{0} x \times \frac{4}{3}e^{2x}dx + \int_{0}^{\infty} x \times \frac{5}{3}e^{-5x}dx$

$$E(x) = \int_{-\infty}^{0} x \times \frac{4}{3}e^{2x}dx + \int_{0}^{\infty} x \times \frac{5}{3}e^{-5x}dx$$

$$\begin{aligned} &= \frac{4}{3} \left[ x \frac{e^{2x}}{2} - 1 x \frac{e^{2x}}{4} \right]_{-\infty}^{0} + \frac{5}{3} \left[ x \frac{e^{-5x}}{(-5)} - 1 x \frac{e^{5x}}{(25)} \right]_{0}^{\infty} \\ &= \frac{4}{3} \left[ \left( 0 - \frac{1}{4} \right) - \left( 0 - 0 \right) \right] + \frac{5}{3} \left[ \left( 0 - 0 \right) - \left( 0 - \frac{1}{25} \right) \right] \end{aligned}$$

$$\begin{aligned} &= \frac{4}{3} \left[ \left( 0 - \frac{1}{4} \right) - \left( 0 - 0 \right) \right] + \frac{5}{3} \left[ \left( 0 - 0 \right) - \left( 0 - \frac{1}{25} \right) \right] \end{aligned}$$

$$\begin{aligned} &= \frac{4}{3} \left[ x \frac{1}{15} - 0.2666 \end{aligned}$$

$$\begin{aligned} &\text{Variance, } V(x) = E(x^{2}) - [E(x)]^{2} \end{aligned}$$

$$\therefore E(x^{2}) = \int_{-\infty}^{\infty} x^{2} x^{4} x^{2} e^{2x} dx + \int_{0}^{\infty} x^{2} x^{5} \frac{5}{3} e^{-5x} dx \end{aligned}$$

$$\begin{aligned} &= \frac{4}{3} \left[ x^{2} \cdot \frac{e^{2x}}{2} - (2x) x \frac{e^{2x}}{4} + 2x \frac{e^{2x}}{8} \right]_{-\infty}^{0} + \frac{5}{3} \left[ x^{2} \cdot \frac{e^{-5x}}{(-5)} - (2x) \frac{e^{-5x}}{(25)} + 2 x \frac{e^{-5x}}{(-125)} \right]_{0}^{\infty} \end{aligned}$$

$$\begin{aligned} &= \frac{4}{3} \left[ \left( 0 - 0 - \frac{2}{8} \right) - \left( 0 - 0 - 0 \right) \right] + \frac{5}{3} \left[ \left( 0 - 0 - 0 \right) - \left( 0 - 0 - \frac{2}{125} \right) \right] \end{aligned}$$

$$\begin{aligned} &= \frac{4}{3} \left[ \left( 0 - 0 - \frac{2}{8} \right) - \left( 0 - 0 - 0 \right) \right] + \frac{5}{3} \left[ \left( 0 - 0 - 0 \right) - \left( 0 - 0 - \frac{2}{125} \right) \right] \end{aligned}$$

$$\begin{aligned} &= \frac{1}{3} + \frac{2}{75} \end{aligned}$$

$$\begin{aligned} &= 0.36 \end{aligned}$$

$$\therefore \text{ Variance } = 0.36 - (-0.2666)^{2} \end{aligned}$$

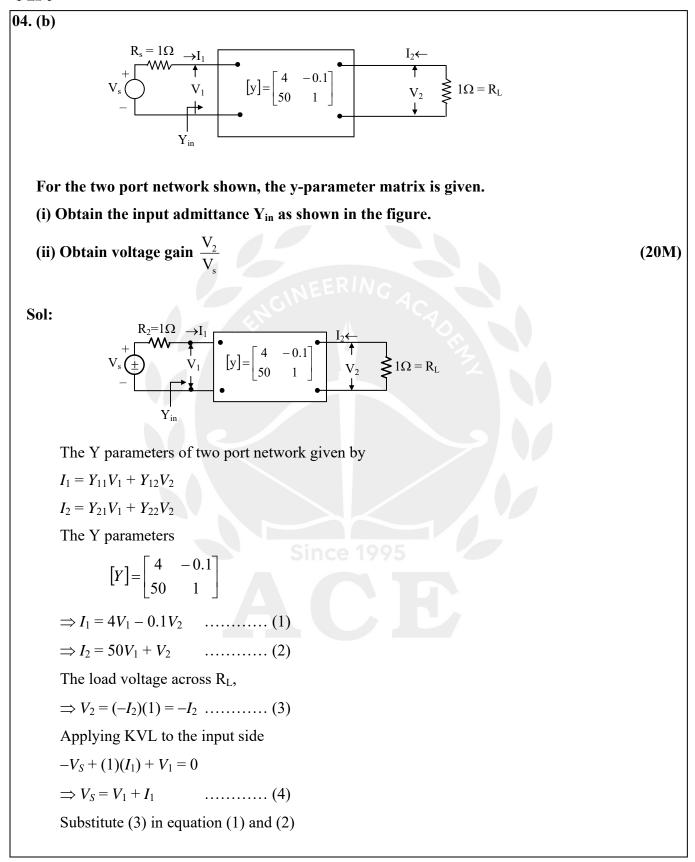

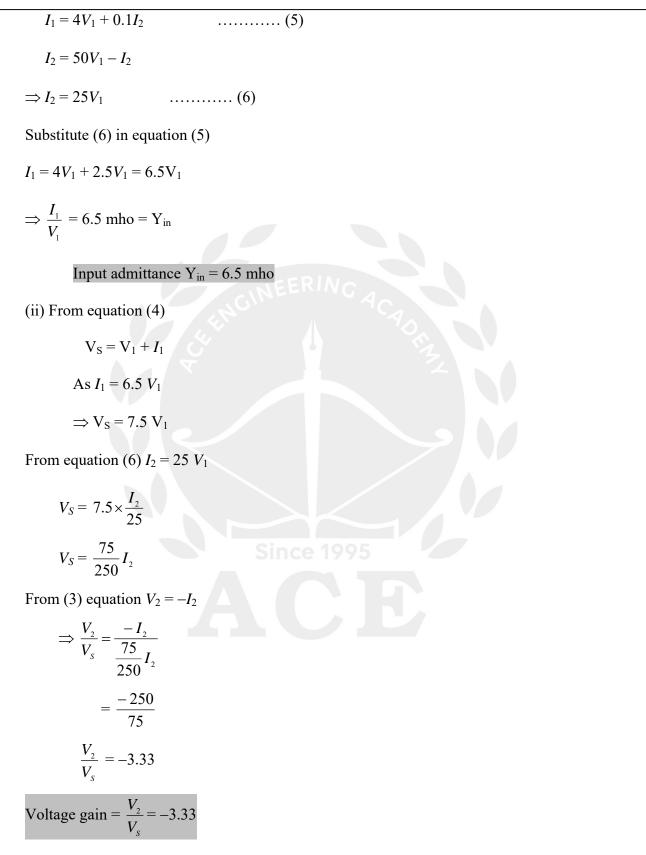

- 04. (c) (i) State whether the given statement is true or false for practical oscillators with reasons. "Loop' gain is generally made slightly larger than unity".

- (ii) In a general form of oscillator circuit given in figure.

Given impedance Z<sub>1</sub>, Z<sub>2</sub> and Z<sub>3</sub> are purely reactive.

Prove that if  $Z_1$  and  $Z_2$  are capacitors then  $Z_3$  must be an inductor and vice versa.

(5+15 M)

Sol: (i) "The given statement is TRUE for practical oscillators"

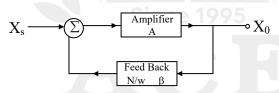

Consider the basic structure of a sinusoidal oscillator i.e. an amplifier with positive feed back as shown in fig.

The overall gain of the amplifier with positive feedback,  $A_f$  is given by  $A_f = \frac{A}{1 - A\beta}$  ..... (1)

<u>Criterion for oscillations</u>: At a specific frequency,  $f_o$ , if the loop gain,  $A\beta$  is equal to unity (i.e.  $A\beta=1$ ), from eq(1),  $A_f$  will be infinite. That is at that frequency,  $f_o$ , the circuit will have a finite output for zero input signal. Such a circuit is called as an oscillator. This condition, loop gain  $A\beta=1$  is called as Barkhausen criterion.

But the Barkhausen Criterion i.e  $A\beta=1$  guarantees sustained oscillations in a mathematical sense only. The gain, A of any physical system is a function of the device

parameters and it is well known that the device parameters are temperature sensitive. Therefore the gain, A cannot be maintained as constant for a long time.

Case(i): Assume that with careful design,  $A\beta$  is maintained at unity in oscillator, so that sustained oscillations are obtained as shown:

Case(ii): Assume that the sudden change in temperature reduces the gain of the system and leads to A $\beta$ , loop gain to fall below unity i.e A $\beta$ <1, which will cause under damped oscillations and over period of time oscillations may be vanished as shown.

Under the circumstances we need a mechanism for forcing  $A\beta$  to remain equal to unity at the desired amplitude of output. This task is accomplished by providing a nonlinear circuit for gain control.

Basically the function of the gain - control mechanism is as follows: First, to ensure that oscillations will start, the circuit is designed such that, the loop gain A $\beta$  is kept at slightly greater then unity this is corresponds to designing the circuit, so that the poles are in the right half of the 'S" plane. Thus, when the oscillations are initiated, the amplitude of oscillations will increases. When the amplitude reaches to the desired level, the non-linear network comes into action and causes the loop gain to be reduced to exactly unity. That is the poles will be pulled back to the j $\omega$  axis. This action will cause the circuit to sustain oscillations at this desired amplitude.

(ii) Step: (1) from the ckt,

$$V_f = \frac{Z_1 V_0}{Z_1 + Z_3}$$

$$\Rightarrow \frac{V_f}{V_o} = \beta = \frac{Z_1}{Z_1 + Z_3}$$

Step (2):  $Z_L = (Z_1 + Z_3)//Z_2$ ~~~  $R_{0r}$ ₹R Ζ Step (3):  $V_0 = \frac{Z_L A V_i}{Z_L + R_0}$  Where A is open loop gain of OP-AMP  $\Rightarrow \frac{V_0}{V_i} = A_V = A \frac{Z_L}{Z_L + R_0}$ Step (4): According to Barkhausen criterion,  $A_V\beta = 1$  $A_{V}\beta = A \left[ \frac{Z_{L}}{Z_{L} + R_{0}} \right] \left[ \frac{Z_{1}}{Z_{1} + Z_{3}} \right] = 1$  $\Rightarrow$  $A\begin{bmatrix} \frac{[z_1 + Z_3]Z_2}{Z_1 + Z_2 + Z_3}\\ \frac{(Z_1 + Z_3)2}{Z_1 + Z_2 + Z_3} + R_0 \end{bmatrix} \begin{bmatrix} \frac{Z_1}{Z_1 + Z_3} \end{bmatrix} = 1$  $\Rightarrow$

$$\Rightarrow A \left[ \frac{\frac{(Z_1 + Z_3)Z_2}{Z_1 + Z_2 + Z_3}}{(Z_1 + Z_3)Z_2 + R_0(Z_1 + Z_2 + Z_3)} \right] \left[ \frac{Z_1}{Z_1 + Z_3} \right] = 1$$

$$\Rightarrow \frac{AZ_{1}Z_{2}}{(Z_{1}+Z_{3})Z_{2}+R_{0}(Z_{1}+Z_{2}+Z_{3})} = 1$$

Step: (5) Let

$$Z_1 = jx_1, Z_2 = jx_2 \& Z_3 = jx_3$$

$$\Rightarrow \frac{-Ax_1x_2}{j(x_1 + x_3)jx_2 + jR_0(x_1 + x_2 + x_3)} = 1$$

$$\Rightarrow \frac{-Ax_1x_2}{-(x_1 + x_3)x_2 + jR_0(x_1 + x_2 + x_3)} = 1 \dots \dots (1)$$

#### Case(i): General equation for frequency of oscillation in LC oscillators:

**NOTE:** Since gain of amplifier is a real value and log gain,  $A\beta$  is also a real value, the imaginary part in equation ( $\beta$ ) is should be zero.

i.e  $X_1 + X_2 + X_3 = 0$  ----- (2)

#### Case (ii): condition for sustained oscillations:

consider the real part in equation (1)

$$\Rightarrow \frac{Ax_1x_2}{(x_1 + x_3)x_2} = 1$$

$$\Rightarrow \frac{Ax_1x_2}{(-x_2)x_2} =$$

$$\therefore A = \frac{-x_2}{-x_2}$$

#### NOTE:

- If Z<sub>1</sub> and Z<sub>2</sub> are capacitors, to satisfy equation (2) & to maintain a phase shift of 180° in the feedback net work, Z<sub>3</sub> should be an inductor.

- (2) If  $Z_1$  and  $Z_2$  are inductors, again to satisfy equation (2) and to establish 180° phase shift in the feed back  $Z_3$  should be a capacitor.

# RANK IMPROVEMENT BATCH EXCLUSIVELY DESIGNED FOR REPEATERS

AND MERITORIOUS STUDENTS

## GATE - 2019 & ESE 2019

### @ DELHI

STREAMS : EC | EE | ME BATCH TYPE : WEEKEND

### MAINS (CIVIL)

EARLY BIRD OFFER **Rs.2000/-** (Till 15<sup>th</sup> July 2018)

CIVIL ENGINEERING REGULAR BATCH : 23<sup>rd</sup> July 2018

: 36 :

# **SECTION - B**

05. (a) Mention the type of Bravais space lattice, relationship of crystal axial lengths (x,y,z) and relationship of interaxial angles (α, β, γ) in the following order of the crystal system.

- (i) Triclinic

- (ii) Monoclinic

- (iii) Orthorhombic and

- (iv) Trigonal

(12M)

# Sol:

| Crystal structure                                | Lattice Parameters                                                         |

|--------------------------------------------------|----------------------------------------------------------------------------|

| 1. Triclinic                                     | $a \neq b \neq c$<br>$\alpha \neq \beta \neq \gamma \neq 90^{\circ}$       |

| 2. Monoclinic                                    | $a \neq b \neq c$<br>$\alpha = \beta = 90^{\circ}, \gamma \neq 90^{\circ}$ |

| 3. Orthorhombic                                  | $a \neq b \neq c$ $\alpha = \beta = \gamma = 90^{\circ}$                   |

| 4. Rhombohedral (trigonal)                       | a = b = c<br>$\alpha = \beta = 90, \gamma \neq 90^{\circ}$                 |

| <sup>1</sup><br>Triclinic <sup>2</sup><br>Simple | <sup>3</sup><br>Simple A A A A A A A A A A A A A A A A A A A               |

Rhombohedral

Same Questions asked in ACE ESE mains 2018 Test Series Mock-1, Q8(a)(i)

monoclinic

Simple

orthorhombic

```

Ingineering Academy

:38:

ESE-2018 Mains (Paper-1)

05.(c) (i)

Write down algorithm in Pseudocode for sorting an array in descending order. Specify

the name of the algorithm you have used.

(6M)

(ii) Write a program segment in any higher level language for Linear search problem.

(Specify which language you are using)

(6M)

Sol: (i)

void sort (array [], n) //size of array is n

{

for i=1 to n, step by 1

Ş

for j=0 to n-i-1

if (Array [j] < Array [j+1])

temp = Array [j];

Array[j] = Array[j+1];

Array [j+1] = temp;

}

The algorithm used is: Bubble sort

Array is having index: 0 to n-1

Array size: n

(ii) Linear search:

Programming language used is C-language

int linear search (Array [], item, n)

{

/* item is the element which is to be searched, n is number of elements in the array, array

has indexed 0 to n-1 */

int i;

```

for (i = 0; i < n; i++)

{

if (Array [i] = = item)

{

return i; /\* for successful search return index of elements\*/

}

}

return -1; /\* for unsuccessful search return -1 \*/

}</pre>

LAST SPARK BATCH for GATE | ESE @ HYDERABAD Starts from 28<sup>th</sup>JUNE 2018 Streams : EC | EE | ME | CE | CSIT

:40:

ACE Engineering Academy

- 05.(e) (i) Explain the electrochemical breakdown in insulators and discuss any two factors that accelerates the breakdown. (8M)

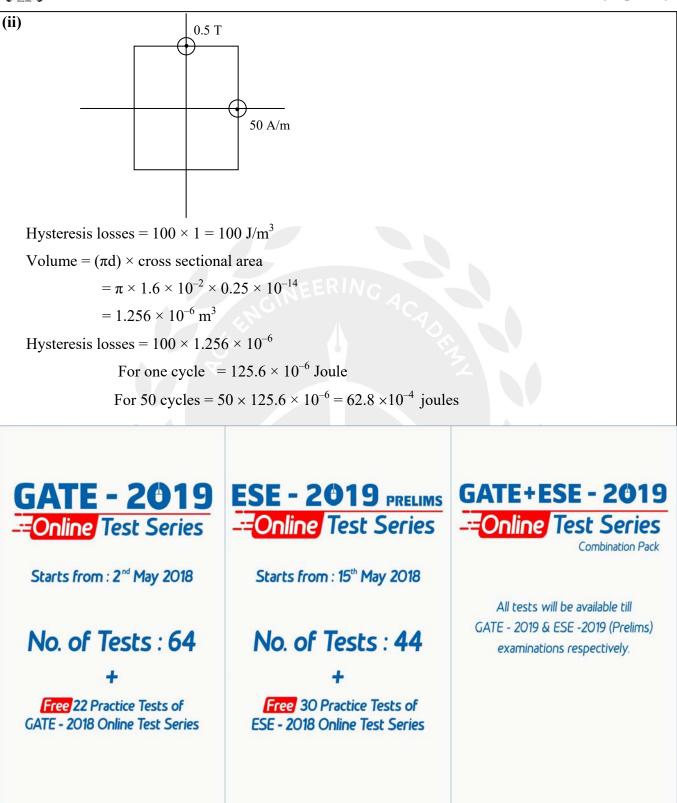

- (ii) A magnetic material having almost a square hysteresis loop has a coercivity of 50 A/m and a remanence of 0.5 T. If this material is used in a toroidal inductor of mean diameter 1.6 cm, with a cross-sectional area of 0.25×10<sup>-4</sup> m<sup>2</sup>, calculate the power loss at a frequency of 50 Hz when the material is driven around one complete hysteresis cycle. (4M)

- **Sol:** Electro-chemical deterioration is due to the presence and mobility of ions in the insulation, which are responsible for leakage current and energy loss in the material. In most of the cases the final breakdown resulting from electro-chemical deterioration is thermal breakdown.

Almost all insulating materials have free ions, which are responsible for leakage current in the presence of electric field. Such ions after reaching the electrodes reduce their charge and may also attack the electrode metal evolving some gas, or some other substance may be deposited on to the electrodes. Such type of activities of the ions are chemically or electrically harmful and many times lead to rapid failure of insulation. The rate of electro-chemical deterioration is determined by the magnitude of leakage current and other factors like concentration of ions in the insulations, temperature, and whether the material is polar one or not. To avoid electro-chemical deterioration:

- (i) The impurities should be avoided in the insulating materials

- (ii) It should not be operated at elevated temperature

- (iii) Care should be taken to avoid contamination in polar materials, which otherwise, will result in high leakage currents.

Detailed solutions are available.

All India rank will be given for each test.

Video solutions are also available for difficult questions. O Comparison with all India toppers of ACE students.

🕓 040 - 48539866 / 040 - 40136222 📓 testseries@aceenggacademy.com

ACE Engineering Academy

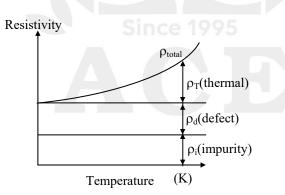

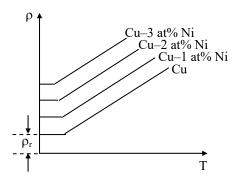

06. (a) (i) Explain electrical resistivity of metals in terms of thermal and residual components. Also draw the schematic variation of them with respect to temperature. (8M)

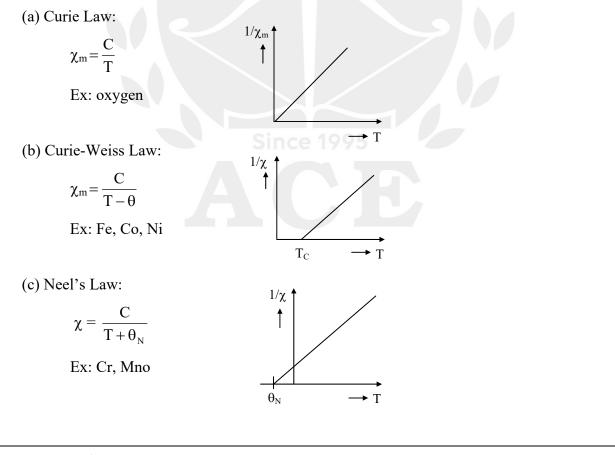

- (ii) Write the relation between magnetic susceptibility and temperature according to Curie Law, Curie-Weiss Law and Neel Law. Sketch the variation of reciprocal of susceptibility with temperature as per the above laws. (6M)

- (iii) What are the ferrites? Mention 3 disadvantages. State the reason, why ferrites are suitable for high frequency operation.

Sol: (i) The thermal component  $\rho_T$ ; which arises from the lattice vibrations, and the residual resistivity  $\rho_r$ , caused by impurities and structural imperfections. The latter is independent of temperature. The total resistivity is given by

$\rho = \rho_T + \rho_r$  .....(1) (Matthiessen's rule)

**Temperature**: The electrical resistance of most metals increases with increase in temperature. At temperatures above the so called Debye temperature, the thermal component of resistivity of conductors is approximately linear.

$\rho \approx \rho_0 \left[1 + \alpha \left(T - T_{RT}\right) + \ldots \right]$

Where  $\rho_0$  is room temperature (T<sub>RT</sub>) resistivity

α is about 0.004 per °C

**Alloying**: A solid solution has a less regular structure than a pure metal. Consequently, the electrical conductivity of a solid solution alloy drops off rapidly with increased alloy content.

$\rho_{alloy} = \rho_{copper} + S\rho_i \quad \mu\text{-ohm-cm}$

Where S = Atomic percentage of added impurity

$\rho i$  = Increases in resistivity for one atomic percent addition of impurity.

**Cold Work:** Mechanical distortion of the crystal structure decreases the conductivity of a metal because the localized strains interfere with electron movement. Thus, hard drawn copper wire has a lower conductivity than annealed copper. Subsequent annealing restores the electrical conductivity by establishing greater regularity in the crystal lattice.

Age Hardening: Age hardening increases the resistivity of an alloy.

(ii) The relation between magnetic susceptibility and temperature

(iii) Ferrite Composition: Ferrites are the important class of magnetic materials containing iron oxide and metal oxides in different ratio depending upon their type. On the basis of their crystal structure, ferrites are of three types namely spinel ferrite, garnet and hexagonal ferrite. There are 3 types of Ferrites:

(a) Spinel Ferrite: A spinel ferrite is a ferromagnetic material, containing mostly iron oxide which is derived from magnetic ( $Fe^{2+}O$ ,  $Fe_2^{2+}O_3$ ) represented by the formula  $M^{2+}$   $Fe_2^{2+}O_4$ . M is a divalent metal iron like cobalt (Co), nickel (Ni), copper (Cu), manganese (Mg), zinc (Zn), cadmium (Cd) etc. Trivalent  $Fe^{3+}$  ions can be replaced by trivalent metal ions like  $Al^{3+}$ ,  $Cr^{3+}$ ,  $Ga^{3+}$  etc. In all cases the ionic radii of the substituting ion should be between 0.5 to 1.0 A.

(b) Garnet Ferrite: The second type of ferrite is a garnet having cubic structure with general formula  $R_2^{3+} Fe_5^{3+}O_{12}$  where R is a rate earth ion (like dysprosium (Dy<sup>3+</sup>), gadolium (Gd<sup>3+</sup>), samarium (Sm<sup>3+</sup>) etc or yttrium (Y<sup>3+</sup>). Fe<sup>3+</sup> can be replaced by trivalent metal ions like Al, Cr, etc.

(c) Magneto-plumbite Ferrite: Magneto-plumbite is having a hexagonal structure and are represented by the formula  $MFe_{12}O_{19}$  where M is a divalent metal ion with large ionic radius like  $Ba^{2+}$ ,  $Sr^{2+}$ ,  $Pb^{2+}$ .

# **Disadvantages:**

- 1. More porocity

- 2. High brittle.

- 3. More cost of production.

# The ferries are used for high frequency applications

- (1) High initial permeability

- (2) High Remanance.

(6M)

06. (b) (i) Prove that the most probable value is the mean value

- (ii) What is an RS-232 interface? How many signals it can handle? How many wires are sufficient for operation? (6M)

- (iii) What is creeping in energy meters? State the reasons for the same and how it is avoided.

**Sol: (i)** Most probable value is mean value:

1. Mean is calculated based upon all the observations in the data.

2. It is amenable to algebraic treatment. The mean of the composite series interms of the means and the sizes of the component series is given by

3. Of all the averages arithmetic mean is affected least by fluctuations of sampling. So that arithmetic mean is a stable average.

4. Sum of deviations of the given values from their mean is always zero.

i.e.,

$$\left(\sum_{i=1}^{n} f_i(x_i - \overline{x}) = 0\right)$$

5. The expected value (mean) is a weighted average of all the possible values of the random variable.

$$\overline{\mathbf{x}} = \mathbf{E}(\mathbf{x}) = \sum_{0}^{n} \mathbf{x} \cdot \mathbf{p}(\mathbf{x}) = \int_{-\infty}^{\infty} \mathbf{x} \cdot \mathbf{f}(\mathbf{x}) d\mathbf{x}$$

$$\sum_{\mathbf{x}=0}^{n} \mathbf{p}(\mathbf{x}) = 1$$

$$\int_{-\infty}^{\infty} \mathbf{f}(\mathbf{x}) d\mathbf{x} = 1$$

Thus we see that arithmetic mean satisfies all the properties laid down by prof. Yule for an ideal average.

(ii) RS-232 interface is standard for the interchange of serial binary data between a DTE (data terminal equipment) such as a computer terminal and a dce (data communication equipment).

The original standard uses 25 wires to connect the two devices.

However, in reality only three of these wires are sufficient.

(iii)In some meters, a slow but continuous rotation is obtained even when there is no current flowing through the current coil and only pressure coil is energized. This is called creeping.

# Causes:

Engineering Academy

- Main reason is Over voltages and over static friction compensation

- Excessive lubrications, vibrations, stray magnetic field of Instrument.

# **Creep error compensation :**

- (i) To eliminate the creeping error, two diametrically opposite holes are drilled in the disc ; the disc will come to rest with one of the holes under the edge of a pole of the shunt magnet.

- (ii) A small piece of iron is attached to the edge of the disc. The force of attraction exerted by the brake magnet on the iron piece is sufficient to prevent creeping of disc.

Same Questions asked in ACE ESE mains 2018 Test Series Test-3, Q3(a), Test-9, Q7(a)

06. (c) (i) Can we use Semiconductor Memory for secondary storage ? Justify your answer. (5M)

- (ii) What exactly is the role of Control Unit in CPU ? How is it different from that of a Arithmetic Logic Unit? (6M)

- (iii) How exactly is an array stored in main memory? Illustrate with the help of storage of a matrix. What will be the exact address of element A (3, 7) of an 8 × 9 array A assuming that location of the first element is d. (9M)

Sol: (i) Yes semiconductor memory can be used as secondary storage.

Now a days most of the Hard disks (Removable) are designed with semiconductor memories with flash technology and pendrive is also used for secondary storage (pendrive uses flash technology).

Flash memory is widely used in advanced cell phones and digital computers.

**Merit:** semiconductor secondary storage memory is faster than other secondary storage memories.

**Demerit:** These are more costlier than other secondary storage.

Note: Example for other secondary memories are magnetic hard disk and CD & DVD.

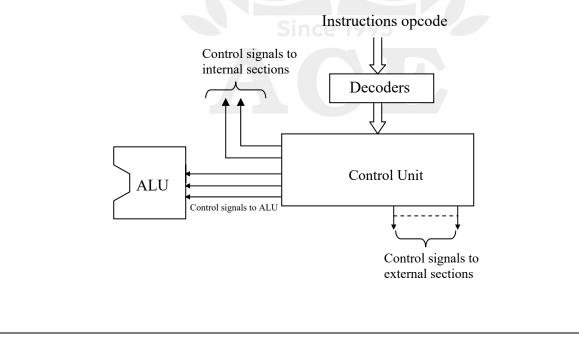

(ii)

ngineering Academy

- Control unit is the hardware inside a CPU for coordinating & controlling the activities of various sub sections within the CPU and other devices connected to the system bus.

- When an instruction is fetched from code memory, its opcode part will be decoded by decoder which produces timing information and control information. The timing information is about further clock cycles required for completing operation & control information is about type of operation to be performed.

The outputs of the decoder will be given to control unit. Then the role of the control unit begins where it generates required control signals to internal sections and external units of CPU. And, inturn operation specified in the opcode will be performed, ALU operation is different from control unit.

- The ALU (Arithmetic Logic Unit) performs various Arithmetic (like addition, subtraction etc). and logical (like AND, OR etc) operations.

- Control unit generates control signals to ALU to decide the type of operation.

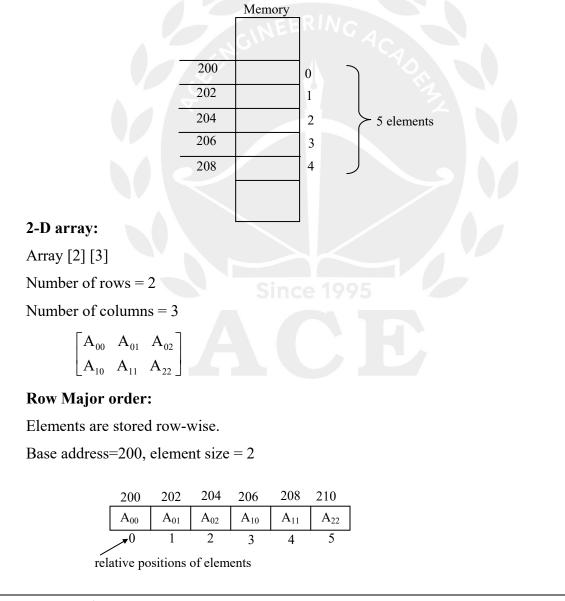

# (iii) Array:

An array is stored in memory on consecutive memory locations

If array is 2-D array: then array storage has 2 types of schemes: Row major order, and column

major order.

1-D array storage:

Array [5]

Suppose each element takes 2 memory locations and base address is 200.

# **Column major order:**

Elements are stored column-wise

|   | 200             | 202             | 204             | 206             | 208             | 210             |

|---|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|   | A <sub>00</sub> | A <sub>10</sub> | A <sub>01</sub> | A <sub>11</sub> | A <sub>02</sub> | A <sub>22</sub> |

| - | 0               | 1               | 2               | 3               | 4               | 5               |

# For the given details:

Array size =  $8 \times 9 = m \times n$

Number of rows (m) = 8

Number of columns (n) = 9

Assuming element size = w

Starting address of array given = d

Starting index = 0

# For row major order:

Address (A [i, j]) = Base + w \* [i \* n + j]

Address (A[3,7]) = d+w\* [3\*9+7] = d+34w

# For column Major order:

Address  $(A[i,j]) = Base + w^* [j * m + i]$

Address (A[3, 7]) = d + w \* [7 \* 7 + 3]

= d + 52w

FOR ESE - MAINS QUALIFIED STUDENTS

# **COURSE HIGHLIGHTS :**

- O Interview Guidance Classes

- O Mock Interviews

- Video Recording

- Feedback Analysis

- O Probable Questions Based on DAF

- O Interview Guidance Material

- O Postal Interview Guidance

- Online Support (Mock Interview through SKYPE)

- O Free Accommodation\* @ Hyderabad & New Delhi .conductors Apply

FOR BATCH DETAILS VISIT : www.aceenggacademy.com

# 4-1-1236/1/A, Sindhu Sadan, King Koti, Abids, Hyderabad – 500001.

Plot No. 3, Kh.No. 264, Kohinoor Enclave, Western Marg, Near Saket Metro Station, Saidulajab, **New Delhi**-110030.

© 7838971777, 9205282120 / 21 / 23 / 24

(6M)

- 07. (a) (i) Supporting with suitable figures, define initial permeability and maximum permeability. Mention the approximate range of values for iron. Mention one importance each of initial and maximum permeabilities. (8M)

- (ii) Specific gravity of a ceramic is 3.2 g/cm<sup>3</sup>. Calculate the percentage apparent porosity and percentage true porosity with the following data:

Ceramic when weighed dry = 360 g

Ceramic when weighed after soaking in water = 385 g

Ceramic weighed while suspended in water = 224 g

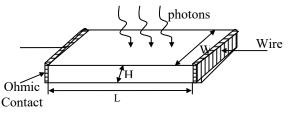

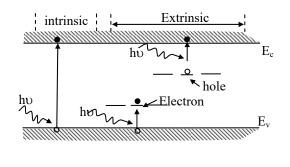

- (iii) What is photo-conductivity? Discuss the factors that are to be considered for the selection of photo-conduction material. (6M)

- Sol: (i) The initial permeability is the limiting value of the core materials permeability at the origin of the magnetization.

$\mu_{i} = \frac{1}{\mu_{0}} \lim_{H \to 0} \frac{B}{H}$

Initial permeability  $\mu_I = tan \theta_1$

Maximum permeability ( $\mu_{max}$ ): The maximum permeability is the value at the core material permeability at high magnetization.

Η

$\mu_{max} = tan \theta_{max}$

$\rightarrow$  The initial permeability of iron is ( $\mu_i$ ) = 1150

$\rightarrow$  The maximum permeability of iron is ( $\mu_{max}$ ) = 61,000

$\rightarrow$  Initial permeability describe the relative permeability of a material of low values of B. The maximum value for permeability is frequently a factor of between 2 and 5 or more above its initial value.

(ii) Given data,

Specific gravity of ceramic = 3.2 g/cm<sup>3</sup> =

$$\rho$$

Ceramic when weighted dry = 360g = W<sub>d</sub>

Ceramic when weighed after soaking in water = 385g = W<sub>w</sub>

Ceramic weighed while suspended in water 224g = W<sub>s</sub>

(1) Percentage apparent porosity =  $\frac{(\text{soaked water} - \text{Dry water})}{(\text{soaked water} - \text{suspended water})} \times 100$

$= \frac{385 - 360}{385 - 224} \times 100$

$= 15.52\%$

(2) Percentage of true porosity =  $\left[1 - \left(\frac{\text{Apparent specific Gravity}}{\text{True specific Gravity}}\right)\right] \times 100$

$= \left(1 - \frac{\text{B}}{\rho}\right) \times 100$

$\text{B} = \frac{W_d}{W_w - W_s} = \frac{360}{385 - 224} = 2.24$

% of true porosity =  $\left(1 - \frac{2.24}{3.2}\right) \times 100 = 30\%$

# (iii) Photoconductivity

• Illumination of an insulating crystal by photons of energy equal to or greater than the band gap  $E_g$  usually excites electrons from the valence band to the conduction band. It makes available the free electrons in the conduction band and the free holes in the valence band, both of which contribute to the electric current under the influence of an external electric field. *This phenomenon is called photoconductivity and is used in light meters (in cameras) and solid state infrared*

Consider semiconducting slab placed in dark. Since a very small current flows in dark, the dark conductivity is

$\sigma_d = ne\mu_e + pe\mu_h \approx 0$

Where n and p are free electron and hole concentrations,  $\mu_e$  and  $\mu_h$  are the electron and hole mobilities, and e is the electron charge. When the electromagnetic radiation of an appropriate frequency is allowed to fall on the semiconductor slab, the electrical conductivity increases, the change in the conductivity (assuming  $\Delta n = \Delta p$ ) is given by

$$\Delta \sigma = \sigma - \sigma_{d} = \Delta n \ e(\mu_{e} + \mu_{h})$$

$$\frac{\Delta \sigma}{\sigma_{d}} = \frac{\Delta n e(\mu_{e} + \mu_{h})}{\sigma_{d}}$$

If " $\tau$ " is the carrier lifetime and *f* is the rate of their generation (i.e. number of electron-hole pairs produced per second by the absorbed photons), then the average photo induced concentration is given by

$\Delta n = f \tau$

Where  $\Delta n = 10^{20} \text{m}^{-3}$  for germanium

In a practical device, the sensitivity is expressed as a gain G.

If 't' is the transit time of the carriers between the electrodes then

$$G = \frac{\tau}{t}$$

Thus, photoconductivity is large when the lifetime is large. A pure material is generally found to have low  $\tau$  ( $\approx 10^{-6}$ s) due to the greater probability of electron hole recombination and hence is relatively insensitive. However a careful doping can suppress recombination and hence increase  $\tau$  and sensitivity.

ama

In CdS careful doping of iodine increases  $\tau$  to  $10^{-3}$  sec.

Iodine substituting for sulphur acts as donor.

Cd<sup>2+</sup> vacancies act as efficient hole traps. During photoexcitation, holes are readily trapped and electron have much less chance of recombination and hence average lifetime is increased CdS and CdTe single crystals are widely used as photoconductors because of their high sensitivity and response to visible light wavelengths.

Model Questions asked in ACE ESE mains 2018 Test Series Test-8, Q4(a)(i).

# TS-NPDCL Online Test Series

Northern Power Distribution Company of Telangana Limited Asst. Engineer ( Electrical )

# No. of Tests : 15

Subject Wise Tests : 12 | Mock Tests : 3

# Starts from **15<sup>th</sup> June 2018** All tests will be available till **15-07-2018**.

🕓 040 - 48539866 / 040 - 40136222 🛛 🗳 testseries@aceenggacademy.com

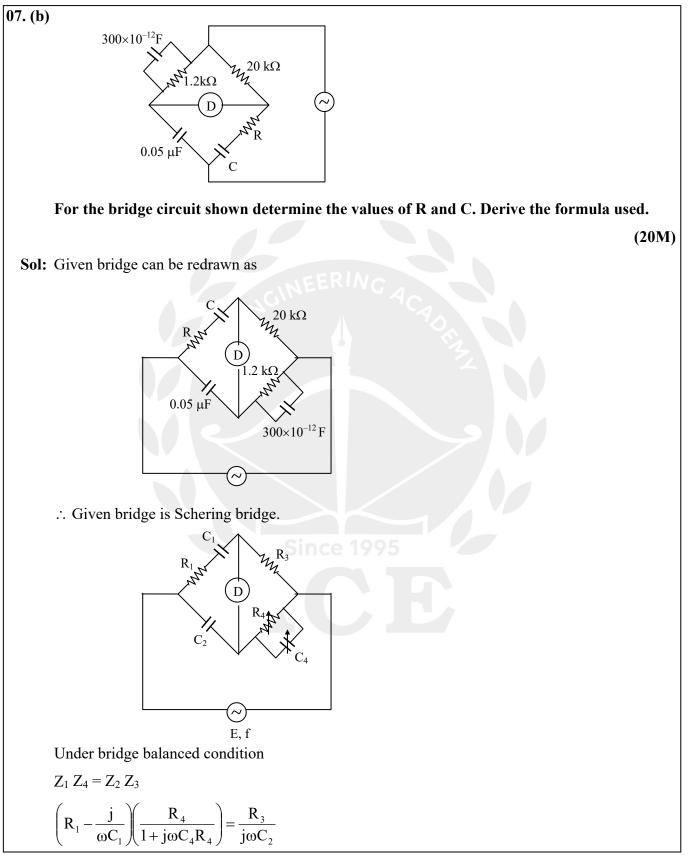

1

$$\left(R_{1} - \frac{j}{\omega C_{1}}\right)(j\omega C_{2}R_{4}) = R_{3}(1 + j\omega C_{4}R_{4})$$

$$j\omega R_{1}R_{4}C_{2} + \frac{C_{2}R_{4}}{C_{1}} = R_{3} + j\omega C_{4}R_{4}R_{3}$$

Equating real parts,

$$\omega C_{2}R/4R_{1} = \omega C_{4}R_{3}R_{4}$$

$$R_{1} = \frac{C_{4}R_{3}}{C_{2}}$$

$$\therefore$$

From the given data, we can write

$$R_{1} = R, C_{1} = C, R_{3} = 20 \text{ k}\Omega, C_{2} = 0.05 \text{ }\mu\text{F}$$

$$R_{4} = 1.2 \text{ }k\Omega, C_{4} = 300 \times 10^{-12} \text{ }\text{F}$$

By substituting in the above equations.

We get, C =

$$\frac{0.05 \times 10^{-6} \times 1.2 \times 10^{3}}{20 \times 10^{3}}$$

C = 3 nF

$$R = \frac{300 \times 10^{-12} \times 20 \times 10^3}{0.05 \times 10^{-6}} = 12 \times 10^{-6} \times 10^3 \times 10^4$$

$R = 120\Omega$

Model Questions asked in ACE ESE mains 2018 Test Series Test-3, Q6(a)

## HEAD OFFICE : HYDERABAD

Sree Sindhi Guru Sangat Sabha Association, # 4-1-1236/1/A, King Koti, Abids, Hyderabad - 500001. Address - II : # 204, Rahman Plaza, Abids, Hyderabad - 500001. Contact No: 040-23234418/19/20, 040-24750437 E-Mail : hyderabad@aceenggacademy.com

## DELHI

Address I : Plot No. 3, Kh.No. 264, Near Saket Metro Station, Saidulajab, New Delhi-110030. Address II : # 63, FNS House, Beside Oriental Bank of Commerce, Near Hauz Khas Metro Station,Kalu Sarai,New Delhi-110016. **Contact No : 9205282121, 9205282123, 7838971777, 9205282120.**

## BHOPAL

# G - 1, Plot no : 207, Zone II, M.P Nagar, M. P - 462013. Contact No: 0755-2554512, 0755-2554612, 0755-4280242

## PUNE

# 302, Vekatesh Villa, Upstairs JANATHA Sahakari Bank, Shivaji Nagar, Pune, Maharashtra - 411005. **Contact No : 020- 25535950, 09343499966**

## BHUBANESWAR

# Plot No: 625/A, 3rd Floor, Janpath, Saheed Nagar, Bhubaneswar. Contact No: 0674-2540340, 9861566244, 09379099966

## LUCKNOW

# A-7, Sector-J, Aliganj, Lucknow, Uttar Pradesh – 226024 Contact No. : 93421 99966, 8081 99 99 66, 0522 4046966

## PATNA

# 1st Floor, N. P. Tower, Kankarbagh, PATNA - 800020. Contact No.: 08252194512, 9308699966, 9212188818

#### **DILSUKH NAGAR**

Gaddiannaram,Dilsukhnagar, Hyderabad. Contact No : 040 - 40209345, 040 - 40044451 KUKATPALLY 2nd floor, BSR Bellezza, Opp : JNTUH Campus, KPHB, Kukatpally, Hyderabad- 500072. Contact No: 040-6597 4465, 040-40199966, 93476 99966

## BENGALURU

# 223, G R Arcade, 2nd floor, Malleswaram, Bangalore - 560003. Contact No: 080-23466699,41526699, 09341299966.

## CHENNAI

# 39, North Usman Road, T Nagar, Chennai - 600017. Contact No: 044 - 42123289, 9343799966

## VISHAKAPATNAM

# Door No. 48-14-91/6, 3rd Floor, Sri Nagar, Visakhapatnam – 530001. Contact No : 0891-6616001, 08374808999

## VIJAYAWADA

# Opp Stella College, Near Benz Circle, Vijayawada – 520 008 Contact No. : 0866-2490001, 96760 76001

TIRUPATI # Plot No:10, AIR Bypass Road, Tirupathi – 517502. Contact No : 0877-2244388, 9618155166, 09341499966

## KOLKATA # 3rd Floor, 369/4, EM Bypass, Avishar Shopping Mall, Kolkata - 700078. Contact No : 8297899966, 8886899966

# www.aceenggacademy.com

: 59 :

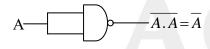

# **07.** (c) (i) How is Division exactly done by ALU?

(ii) Prove with illustration that NAND is a "Universal Gate".

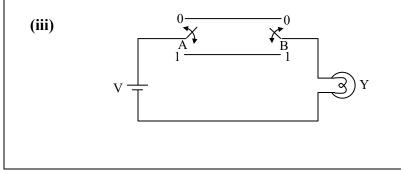

(iii) How will you implement a two-way switch using minimum number of logic gates?

(7M)

(7M)

(6M)

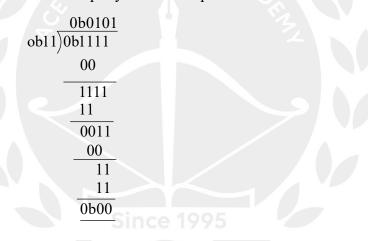

# Sol: (i) Integer Division

Division is implemented using computer specific methods. Division can be implemented on computer systems by repeatedly subtracting the divisor from the dividend and counting the number of times that the divisor can be subtracted from the dividend before the dividend becomes smaller than the divisor. For example, 15 can be divided by 5 by subtracting 5 repeatedly from 15, getting 10, 5 and 0 as intermediate result. The quotient, 3, is the number of subtractions that had to be performed before the intermediate result became less than the dividend. Below shown an exemplary division steps for  $15 \div 5$ .

# An Example of Division steps for 15 ÷ 5 Restoring Algorithm

The following algorithm, called the restoring algorithm for a division, can be used. Assume that

X register has k-bit dividend and Y has the k-bit divisor. Assume a sign bit S has the sign.

- Start: Load 0 into accumulator k-bit A and dividend X is loaded into the k-bit quotient register MQ.

- 2. Step A: Shift 2k-bit registers pair A- MQ left.

- 3. Step B: Subtract the divisor Y from A.

- 4. Step C: If sign of A (msb) = 1, then reset  $MQ_0$  (lsb) = 0 else set = 1

- 5. Step D: If  $MQ_0=0$  add Y (restore the effect of earlier subtraction).

- 6. Steps A to D repeat again till the total number of cyclic operations = k.

- 7. At the end, A has the remainder and MQ has the quotient.

| Step    | S-flag* | First<br>Register<br>for A | Second<br>Register<br>for MQ | Action Taken                                                                                     | Number of operations<br>(instructions) |

|---------|---------|----------------------------|------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------|

| Start   | 0       | 0b 0000                    | 0b 0000                      | Clear S, A, MQ                                                                                   | 3 for clearing C,<br>A and M           |

|         | 0       | 0Ь 0001                    | 0Ь 1110                      | Load dividend X (lower k bits)<br>between $MQ_{k-1}$ and $MQ_0$ and<br>dividend higher bits in A | 2 for loading A and MQ                 |

| Step 0A | 0       | 0011                       | 1100                         | Shift left S-A-M                                                                                 | 2                                      |

| Step 0B | 0       | 0000                       | 1100                         | Subtract Y from S-A, result in S-A                                                               | 1                                      |

| Step 0C | 0       | 0000                       | 1101                         | $MQ_0 = 1 \text{ as } S = 0$                                                                     | 1                                      |

| Step 0D | 0       | 0000                       | 1101                         | Skip restore by adding as $S = 0$                                                                | 1 (test S)                             |

| Step 1A | 0       | 0001                       | 1010                         | Shift left S-A-M                                                                                 | 2                                      |

| Step 1B | 1       | 1110                       | 1010                         | Subtract Y from S-A, result in S-A                                                               | 1                                      |

| Step 1C | 1       | 1110                       | 1010                         | $MQ_0 = 0 \text{ as } S = 1$                                                                     | 1                                      |

| Step 1D | 0       | 0001                       | 1010                         | Add Y into S-A to restore as S= 1                                                                | 1                                      |

| Step 2A | 0 🖌     | 0011                       | 0100                         | Shift left S-A-M                                                                                 | 2                                      |

| Step 2B | 0       | 0000                       | 0100                         | Subtract Y from S-A, result in S-A                                                               | 1                                      |

| Step 2C | 0       | 0000                       | 0101                         | $MQ_0 = 1 \text{ as } S = 0$                                                                     | 1                                      |

| Step 2D | 0       | 0000                       | 0101                         | Skip restore as S = 0                                                                            | 1(test S)                              |

| Step 3A | 0       | 0000                       | 1010                         | Shift left S-A-M                                                                                 | 2                                      |

| Step 3B | 1       | 1101                       | 1010                         | Subtract Y from S-A, result in S-A                                                               | 1                                      |

| Step 3C | 1       | 1101                       | 1010                         | $MQ_0 = 0 \text{ as } S = 1$                                                                     | 1                                      |

| Step 3D | 0       | 0000                       | 1010                         | Add Y into S–A to restore as $S = 1$                                                             | 1                                      |

| Answer  | 0       | Remaind                    | er = 0                       | Quotient Decimal 10                                                                              | Total 25                               |

\* after the left shift from msb of A.

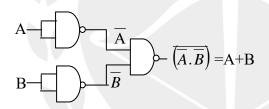

(ii) If it is possible to implement any logic function using only the basic gates, then the gate is called universal.

To implement any logic function the basic function required is OR, AND and NOT gates. If it is possible to implement there three basic gates using only the gates then it is possible implement any logic function.

(1) Realization of AND gate using NAND gate:

$$A \longrightarrow \overline{AB} \longrightarrow \overline{AB} = AB$$

(2) Realization of OR gate using NAND gate:

(3) Realization of NOT gate using NAND gate:

... NAND gate is universal gate

# ESE / GATE / PSUs - 2019 ADMISSIONS OPEN

| CENTER                 | COURSE                       | BATCH TYPE           | DATE                |

|------------------------|------------------------------|----------------------|---------------------|

| HYDERABAD - DSNR       | GATE + PSUs - 2019           | <b>Regular Batch</b> | 8th, 22nd July 2018 |

| HYDERABAD - Kukatpally | GATE + PSUs - 2019           | <b>Regular Batch</b> | 2nd July 2018       |

| HYDERABAD - Abids      | GATE + PSUs - 2020           | Morning Batch        | 15th July 2018      |

| HYDERABAD - DSNR       | GATE + PSUs - 2020           | Morning Batch        | 22nd July 2018      |

| HYDERABAD - Kukatpally | GATE + PSUs - 2020           | Morning Batch        | 22nd July 2018      |

| HYDERABAD - DSNR       | GATE + PSUs - 2020           | <b>Evening Batch</b> | 22nd July 2018      |

| HYDERABAD - Kukatpally | GATE + PSUs - 2020           | <b>Evening Batch</b> | 22nd July 2018      |

| HYDERABAD - DSNR       | ESE + GATE + PSUs - 2019     | Regular Batch        | 8th, 22nd July 2018 |

| HYDERABAD - Abids      | ESE + GATE + PSUs - 2020     | Morning Batch        | 15th July 2018      |

| HYDERABAD - DSNR       | ESE + GATE + PSUs - 2020     | Morning Batch        | 22nd July 2018      |

| HYDERABAD - Kukatpally | ESE + GATE + PSUs - 2020     | Morning Batch        | 22nd July 2018      |

| HYDERABAD - DSNR       | ESE + GATE + PSUs - 2020     | <b>Evening Batch</b> | 22nd July 2018      |

| HYDERABAD - Kukatpally | ESE + GATE + PSUs - 2020     | <b>Evening Batch</b> | 22nd July 2018      |

| HYDERABAD - Abids      | ESE - 2019 ( PRELIMS ) - G.S | Regular Batch        | 09th July 2018      |

| DELHI                  | GATE + PSUs - 2019           | Regular Batch        | 22nd July 2018      |

| PUNE                   | GATE + PSUs - 2019           | Weekend Batch        | 07th July 2018      |

| PUNE                   | GATE + PSUs - 2020           | Weekend Batch        | 04th Aug 2018       |

| PUNE                   | ESE + GATE + PSUs - 2020     | Weekend Batch        | 04th Aug 2018       |

| BHUBANESWAR            | GATE + PSUs - 2019           | Regular Batch        | 07th July 2018      |

| CHENNAI                | GATE + PSUs - 2019           | Weekend Batch        | 07th July 2018      |

| CHENNAI                | GATE + PSUs - 2019           | <b>Regular Batch</b> | 07th July 2018      |

| CHENNAI                | GATE + PSUs - 2020           | Weekend Batch        | 07th July 2018      |

| BANGALURU              | GATE + PSUs - 2019           | Weekend Batch        | 07th July 2018      |

| BANGALURU              | GATE + PSUs - 2020           | Weekend Batch        | 07th July 2018      |

| PATNA                  | GATE + PSUs - 2020           | Weekend Batch        | 14th July 2018      |

| VISAKHAPATNAM          | GATE + PSUs - 2019           | <b>Regular Batch</b> | 17th July 2018      |

| VISAKHAPATNAM          | GATE + PSUs - 2020           | Weekend Batch        | 08th July 2018      |

| TIRUPATI               | GATE + PSUs - 2020           | Weekend Batch        | 14th July 2018      |

FOR BATCH DETAILS VISIT : www.aceenggacademy.com

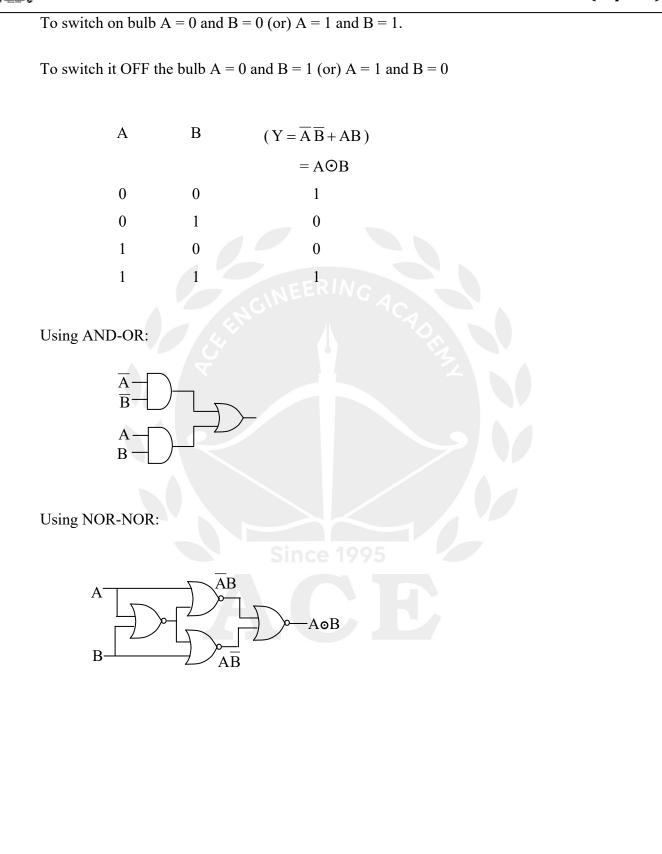

- 08.(a) (i) Explain the Top-Bottom and Bottom-Up approach to produce the nanostructure. Name the methods used in each case to produce nanomaterial. (8M)

- (ii) The current measured in a superconducting ring by 0.01% accuracy meter after one year shows no decay of current. If there are  $10^{28}$  electrons/m<sup>3</sup>, calculate the conductivity. How may times larger is this conductivity than that of copper of resistivity  $1.724 \times 10^{-8} \Omega m$ . (8M)

- (iii) Addition of 0.25 atomic percent nickel and 0.4 atomic percent silver into copper at 298 K increases the resistivity by 0.012  $\mu\Omega$ cm and 0.016  $\mu\Omega$ m respectively. If the resistivity of copper is 0.015  $\mu\Omega$ m at 298 K, determine the conductivity of the resulting alloy. (4M)

Sol:

(i) Top down Approach:

Engineering Academy

- Top down approach refers to slicing or successive cutting of a bulk material to get nano sized particle.

- Attrition or Milling is a typical top down method in making nano particles

- The nanomaterials are derived form a bulk substrate and obtained by progressive removal of material, until the desired nanomaterial is obtained.

- This approach leads to the bulk production of nano material. Regardless of the defects produced by top down approach, they will continue to play an important role in the synthesis of nano structures.

- **Ex:** (1) photo lithography

- (2) Scanning lithography

- (3) E- beam lithography

# **Photo Lithography:**

This technique follows the principle of transferring an image from a mask to a receiving substrate.

A typical lithographic process consists of three successive steps:

- Coating a substrate (Si wafer or glass) with a sensitive polymer layer (called resist)

- Exposing the resist to light, electrons or ion beams

- Developing the resist image with a suitable chemical(developer), which reveals a positive or negative image on the substrate depending on the type of resist used.( i.e. positive tone or negative tone resist).

## Problems associated with top down approach:

- The biggest problem with top down approach is the imperfection of surface structure and significant crystallographic damage to the processed patterns. Due to these imperfections design and fabrication of devices is difficult.

- The top down approach introduces internal stress, in addition to surface defects and contaminations

## **Bottom up Approach:**

# Since 1995

- Bottom up approach refers to the build up of a material from the bottom; atom by atom, molecule by molecule or cluster by cluster.

- The *colloidal dispersion* is a good example of bottom up approach in the synthesis of nano particles.

- This method is not a new concept. All the living beings in nature observe growth by this approach only and also it has been in industrial use for over a century.

Ex: The production of salt and nitrate in chemical industry.

- Bottom up approach gives a better chance to obtain nano structures with less defects, more homogeneous chemical composition.

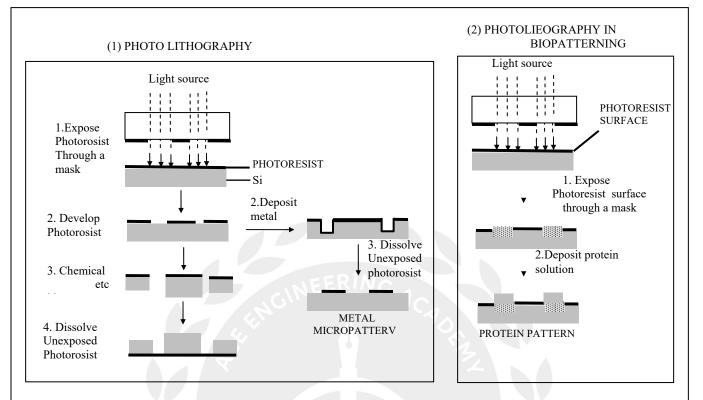

- Bottom up methods can be divided into gas-phase and liquid-phase methods.

## Gas-phase methods:

Plasma arcing and chemical vapour deposition

# Liquid phase methods:

Sol-gel synthesis, molecular self-assembly

# Chemical vapour deposition:

The material to be deposited is first heated to its gas form and then allowed to deposit as a solid on a surface.

- The method is normally performed under vacuum.

- The deposition can be direct or through a chemical reaction so that the material deposited is different from the one volatilized.

- This process is routinely used to make nanopowders of oxides and carbides of metals if carbon or oxygen are present with the metal.

- The method can also be used to generate nanopowders of pure metals, although not so easily.

- Chemical vapour deposition is often used to deposit a material on a flat surface.

- When a surface is exposed to a chemical vapour, the first layer of atoms or molecules that deposit on the surface can act as a template on which material can grow.

Model Questions asked in ACE ESE mains 2018 Test Series Test-7, Q4(c).

(ii) Given data,

$$n = 10^{28} \text{ elec/m}^3$$

$e = 1.6 \times 10^{-19}$

$\rho = 1.724 \times 10^{-8} \ \Omega m$

Let us assume that the super conducting ring relaxation time (t) =  $3.15 \times 10^{11}$  sec

Electrical conductivity ( $\sigma$ ) =  $\frac{ne^2t}{m}$

$$=\frac{10^{28} \times (1.6 \times 10^{-19})^2 \times 3.15 \times 10^{11}}{9.1 \times 10^{-31}}$$

$$= 0.883 \times 10^{32} \text{ n-m}^{-1}$$

Electrical conductivity of copper ( $\sigma$ ) =  $\frac{1}{\rho} = \frac{1}{1.724 \times 10^{-8}}$

$$= 0.58 \times 10^8 \text{ n-m}^{-1}$$

The electrical conductivity of super conducting ring is  $1.5278 \times 10^{24}$  larger than copper.

# (iii) Given data,

Host material = cu

$\rho_{cu} = 0.015 \ \mu\Omega \ km$

Impurity materials are Ni & Ag

Atomic percent of Ni added to cu is  $(S_{Ni}) = 0.25$

Atomic percent of Ag added to cu is  $(S_{cu}) = 0.4$

Increase in resistivity of Ni  $(\rho_{Ni}) = 0.012 \ \mu\Omega \ m$

Increase in resistivity of Ag ( $\rho_{Ag}$ ) = 0.016  $\mu\Omega$

$\rho_{alloy} = \rho_{cu} + S_{Ni} \ \rho_{Ni} + S_{Ag} \ \rho_{Ag}$

= 0.015 + 0.25(0.012) + 0.4(0.016)

$= 0.0244 \ \mu\Omega m$

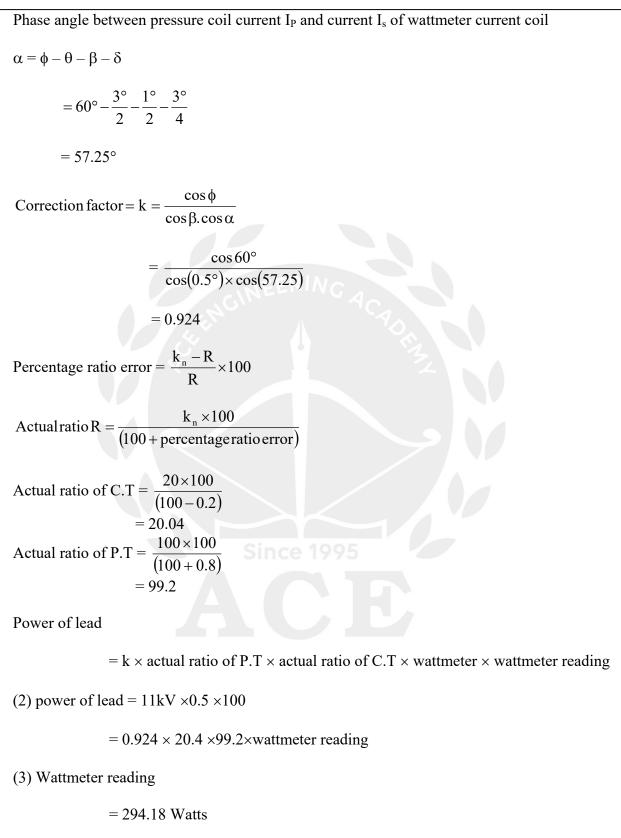

| 08. (b) | The power consumed by a single phase 11 kV load taking 100 A at 0.5 power factor lagging                           |

|---------|--------------------------------------------------------------------------------------------------------------------|

|         | is measured on a dynamometer wattmeter used in conjunction with potential transformer                              |

|         | (PT) and current transformer (CT). Determine the reading of the wattmeter considering                              |

|         | the following data:                                                                                                |

|         | Nominal ratio of PT and CT are 100: 1 and 20: 1                                                                    |

|         | Ratio error of PT and CT are +0.8% and -0.2%                                                                       |

|         | Phase angle errors of PT and CT are +42 minutes and +90 minutes.                                                   |

|         | Phase angle of the pressure coil due to its inductance is 30 minutes. (20M)                                        |

|         |                                                                                                                    |

| Sol:    | Phase angle of pressure coil circuit ( $\beta$ ) = 30'                                                             |

|         | Phase angle of load = $\cos^{-1}(0.5) = 60^{\circ}$                                                                |

|         | Where                                                                                                              |

|         | V = voltage across the load = 11 kV                                                                                |

|         | I = load current = 100A                                                                                            |

|         | $\phi$ = Phase angle between current and voltage = 60°                                                             |

|         | $\alpha$ = phase angle bandwidth                                                                                   |

|         | Currents in the current and pressure coils of watt meter                                                           |

|         | $V_s$ = voltage across secondary of the potential transformer.                                                     |

|         | $I_s$ = secondary current of current transformer.                                                                  |

|         | $I_p$ = current in the wattmeter pressure coil.                                                                    |

|         | $\beta$ = angle by which I <sub>s</sub> lags V <sub>s</sub> on account of inductance of pressure coil = 30' = 1/2° |

|         | $\delta$ = Phase angle of potential transformer = $45' = \frac{3}{4}^{\circ}$                                      |

|         | $\theta$ = phase angle of current transformer = 90' = $1\frac{1}{2}^{\circ}$                                       |

:70:

08.(c) (i) Is the use of Virtual Memory advisable for Real Time Systems? Justify briefly your<br/>answer(7M)(ii) Compare briefly and precisely the LINUX OS with Windows-NT OS.(5M)(iii) For File Management how does a DBMS help?(8M)

# Sol:

- (i) Generally speaking, RTOS and VM are mutually exclusive. The RT in RTOS stands for "Real Time", meaning that the OS has a quick (and deterministic) task swap time and IRQ latency. You can't really have that when some of your memory is located in Flash/SSD/HD and might have to be swapped into main memory.

- **(ii)**

| Topics | Linux                            | Windows                           |

|--------|----------------------------------|-----------------------------------|

| Price  | The Linux kernel, and the        | Microsoft Windows usually costs   |

|        | GNU utilities and libraries      | between \$99.00 and \$199.00 USD  |

|        | which accompany it in most       | for each licensed copy. However,  |

|        | distributions, are entirely free | Windows 10 is being offered as a  |

|        | and open source. You can         | free upgrade to current owners of |

|        | download and install             | Windows 7 or Windows 8.1.         |

|        | GNU/Linux distributions          |                                   |

|        | without purchase. Some           | 5                                 |

|        | companies offer paid support     | 5                                 |

|        | for their Linux distributions,   |                                   |

|        | but the underlying software is   |                                   |

|        | still free to download and       |                                   |

|        | install.                         |                                   |

# **Electrical Engineering**

| Ease of     | CNUL/Linux operating systems   | Windows is one of the easiest          |

|-------------|--------------------------------|----------------------------------------|

|             | GNU/Linux operating systems    |                                        |

| use         | have a steeper learning curve  | desktop operating systems to use.      |

|             | for the average user. They     | One of its primary design              |

|             | frequently require a deeper    | characteristics is user friendliness   |

|             | understanding of the           | and simplicity of basic system tasks.  |

|             | underlying system to perform   | Its ease lack                          |

|             | day-to-day functions.          | of difficulty is considered a positive |

|             | Additionally,                  | by users who want their system to      |

|             | troubleshooting technical      | just work. However, more proficient    |

|             | issues can be a more           | users may be frustrated by             |

|             | intimidating and complicated   | oversimplification of system tasks at  |

|             | process than on Windows.       | the expense of fine-grained control    |

|             | However, some distributions    | over the system itself.                |

|             | such as Ubuntu and Linux       |                                        |

|             | Mint are designed specifically |                                        |

|             | to ease the transition from    |                                        |

|             | Windows to a Linux             |                                        |

|             | environment.                   |                                        |

| Reliability | Linux is notoriously reliable  | Although Microsoft Windows has         |

|             | and secure. It has a strong    | made great improvements in             |

|             | focus on process management,   | reliability in recent years, it's      |

|             | system security, and uptime.   | considered less reliable than          |

|             |                                | Linux. Many of the sacrifices it       |

|             |                                | makes in the name of user-             |

|             |                                | friendliness can lead to security      |

|             |                                | vulnerabilities and system             |

|             |                                | instability.                           |

# ESE-2018 Mains (Paper-1)

| Software | There thousands of programs       | Windows commands the highest         |

|----------|-----------------------------------|--------------------------------------|

|          | available for Linux, and many     | number of desktop users, and         |

|          | are available as easy-to-install  | therefore the largest selection of   |

|          | software packages — all for       | commercial software. It also has the |

|          | free. Also, many Windows          | largest selection of video games by  |

|          | programs can be run on Linux      | a wide margin.                       |

|          | using compatibility layers such   |                                      |

|          | as WINE. Linux supports a         |                                      |

|          | wider array of free software      |                                      |

|          | than Windows.                     |                                      |

| Hardware | Fifteen years ago, Linux          | Windows has a massive user base, so  |

|          | struggled to support new          | it would be madness for              |

|          | hardware. Manufacturers often     | a consumer hardware manufacturer     |

|          | considered Linux support a        | not to support Windows. As a         |

|          | secondary concern (if they        | Windows user, you can rest assured   |

|          | considered supporting it at all). | that your operating system is        |